# MULTIBAND ANALOG-TO-DIGITAL CONVERSION

By

Scott Saucier

B.S. University of Maine, 2000

#### A THESIS

Submitted in Partial Fulfillment of the

Requirements for the Degree of

Master of Science

(in Electrical Engineering)

The Graduate School

The University of Maine

December, 2002

## **Advisory Committee:**

Donald M. Hummels, Professor of Electrical and Computer Engineering, Advisor Fred H. Irons, Professor Emeritus of Electrical and Computer Engineering David E. Kotecki, Associate Professor of Electrical and Computer Engineering

# LIBRARY RIGHTS STATEMENT

| In presenting this thesis in partial fulfillment of the requirements for an advanced       |

|--------------------------------------------------------------------------------------------|

| degree at The University of Maine, I agree that the Library shall make it freely available |

| for inspection. I further agree that permission for "fair use" copying of this thesis for  |

| scholarly purposes may be granted by the Librarian. It is understood that any copying      |

| or publication of this thesis for financial gain shall not be allowed without my written   |

| permission.                                                                                |

| Signature: |

|------------|

|------------|

Date:

MULTIBAND ANALOG-TO-DIGITAL

CONVERSION

By Scott Saucier

Thesis Advisor: Dr. Donald M. Hummels

An Abstract of the Thesis Presented in Partial Fulfillment of the Requirements for the Degree of Master of Science (in Electrical Engineering) December, 2002

The current trend in the world of digital communications is the design of versatile devices that may operate using several different communication standards in order to increase the number of locations for which a particular device may be used. The signal is quantized early on in the reciever path by Analog-to-Digital Converters (ADCs), which allows the rest of the signal processing to be done by low complexity, low power digital circuits. For this reason, it is advantageous to create an architecture that can quantize different bandwidths at different frequencies to suit several different communication protocols.

This thesis outlines the design of an architecture that uses multiple ADCs in parallel to quantize several different bandwidths of a wideband signal. A multirate filter bank is then applied to approximate perfect reconstruction of the wideband signal from its subband parts. This highly flexible architecture is able to quantize signals of varying bandwidths at a wide range of frequencies by using identical hardware in every channel, which also makes for a simple design. A prototype for the quantizer used in each channel, a frequency-selective fourth-order sigma-delta ( $\Sigma\Delta$ ) ADC, was designed and fabricated in a 0.5  $\mu$ m CMOS process. This device uses a switched-capacitor technique to implement the frequency selection in the front-end of the  $\Sigma\Delta$  ADC in each channel. Running at a 5MHz sample rate, the device can select any of the first sixteen 156.25kHz wide bands for conversion. Testing results for this fabricated part are also presented.

#### ACKNOWLEDGMENTS

Part of this research was funded by the Roger Castle Fund. The assistance has been greatly appreciated.

I would first like to thank my parents, Mr. and Mrs. Gaelen Saucier for their support during my long academic career here at the University of Maine. I would also like to thank my brother Tony for being such a great friend these last few years. I would especially like to thank my wife Erin for her patience and encouragement throughout the entire process.

Many thanks go to my advisor Don Hummels, whose ideas and guidance were key to the development of this project. Thanks also to Fred Irons, for his help with this thesis, with other projects both at the undergraduate and graduate levels, and with fishing. Thanks to Dave Kotecki for serving on this committee and for his help during the design and layout of the prototype hardware. Thanks to Ron Bryant for undertaking the design of the hardware for this project with me. And last but not least, thanks to Kannan Sockalingam for suffering through Graduate School these last two years with me and for being a great friend.

This work is dedicated to the memory of my grandfather Gayland A. Moore Jr., one of the first engineers I ever knew.

# TABLE OF CONTENTS

| ACKNOWLEDGMENTS i |        |        |                                                 | ii |

|-------------------|--------|--------|-------------------------------------------------|----|

| L                 | IST O  | F TAB  | LES                                             | v  |

| L                 | IST O  | F FIGU | URES                                            | vi |

| Cl                | napter |        |                                                 |    |

| 1                 | INT    | RODU   | CTION                                           | 1  |

|                   | 1.1    |        | ground                                          |    |

|                   |        | 1.1.1  | Time-interleaved structure                      |    |

|                   |        | 1.1.2  | Frequency analysis structure                    |    |

|                   |        | 1.1.3  | $\Sigma\Delta$ ADCs used for channel quantizers |    |

|                   | 1.2    | Purpo  | se of the research                              |    |

|                   | 1.3    | -      | s organization                                  |    |

| 2                 | BAN    | DPASS  | S SIGNALS                                       | 7  |

|                   | 2.1    | Comp   | lex representation of bandpass signals          | 7  |

|                   |        | 2.1.1  | Complex modulation                              | 8  |

|                   |        | 2.1.2  | Properties of bandpass representations          | 11 |

|                   | 2.2    | Bandp  | pass sampling schemes                           |    |

|                   |        | 2.2.1  | IQ ADC structure                                | 12 |

|                   |        | 2.2.2  | Subsampling IQ structure                        | 13 |

|                   |        | 2.2.3  | $\Sigma\Delta$ bandpass sampling                | 16 |

|                   |        | 2.2.4  | $\Sigma\Delta$ IQ structure                     | 17 |

|                   | 2.3    | Propo  | sed structure                                   | 17 |

| 3                 | FILT   | ERIN   | G                                               | 21 |

|                   | 3.1    | Digita | l filter banks                                  | 21 |

|                   |        | 3.1.1  | Uniform DFT filter banks                        |    |

|                   |        | 3.1.2  | Quadrature mirror filter banks                  | 24 |

|                   | 3.2    |        | rate filter bank for signal reconstruction      |    |

|                   |        | 3.2.1  | Band demodulation                               | 28 |

|                   |        | 3.2.2  | Filtering and sample rate conversion            | 29 |

|                   |        | 3.2.3  | Recombination stage                             | 35 |

|                   |        | 3.2.4  | Filter design                                   | 37 |

|                   |        |        | 3.2.4.1 Multistage decimation                   | 39 |

|                   |        |        | 3.2.4.2 Half-band filters                       | 40 |

|                   |        | 3.2.5  | Signal delay                                    | 43 |

|                   | 3.3    | Filter | bank design summary                             | 46 |

| 4 | ARC                     | RCHITECTURE DESIGN                              |    |  |  |

|---|-------------------------|-------------------------------------------------|----|--|--|

|   | 4.1                     | Channel ADCs                                    | 48 |  |  |

|   |                         | 4.1.1 Frequency selective IQ $\Sigma\Delta$ ADC | 48 |  |  |

|   |                         | 4.1.2 Division of channels                      | 49 |  |  |

|   | 4.2                     | Filter designs                                  | 49 |  |  |

|   |                         | 4.2.1 Decimation filtering                      | 49 |  |  |

|   |                         | 4.2.2 Interpolation filtering                   | 55 |  |  |

|   | 4.3                     | Recombination performance                       | 57 |  |  |

|   |                         | 4.3.1 Filter bank performance                   | 57 |  |  |

|   |                         | 4.3.2 Sampling architecture performance         | 63 |  |  |

|   | 4.4                     | Conclusions                                     | 65 |  |  |

|   |                         |                                                 |    |  |  |

| 5 | FRE                     | QUENCY-SELECTIVE $\Sigma\Delta$ MODULATOR       | 68 |  |  |

|   | 5.1                     | Project goals                                   | 68 |  |  |

|   | 5.2                     | $\Sigma\Delta$ ADC basics                       | 69 |  |  |

|   |                         | Chip specifications                             | 73 |  |  |

|   | 5.4                     | Major components                                | 74 |  |  |

|   |                         | 5.4.1 Second-order $\Sigma\Delta$ loop          | 74 |  |  |

|   |                         | 5.4.2 IQ modulator                              | 76 |  |  |

|   | 5.5                     |                                                 |    |  |  |

|   | 5.6                     |                                                 |    |  |  |

|   |                         | 5.6.1 Baseband test                             | 84 |  |  |

|   |                         | 5.6.2 Adjacent band tests                       | 88 |  |  |

|   | 5.7                     | Conclusions                                     | 89 |  |  |

| 6 | CON                     | ICLUSIONS                                       | 92 |  |  |

|   | 6.1                     | Proposed architecture                           | 92 |  |  |

|   | 6.2                     | Channel quantization device                     | 93 |  |  |

| R | EFER                    | ENCES                                           | 94 |  |  |

| B | BIOGRAPHY OF THE AUTHOR |                                                 |    |  |  |

# LIST OF TABLES

| 3.1 | Requirements of the interpolation filter for different rates of decimation |    |

|-----|----------------------------------------------------------------------------|----|

|     |                                                                            | 38 |

| 3.2 | Phase shift factor coefficients for 4 stages of an $M$ -channel system     | 45 |

| 4.1 | Filter specifications                                                      | 56 |

| 5.1 | Device specifications for the ADC of [1]                                   | 73 |

| 5.2 | Modulator capacitor and subunit values                                     | 80 |

| 5.3 | Test conditions for performance evaluation of the fabricated device        | 84 |

# LIST OF FIGURES

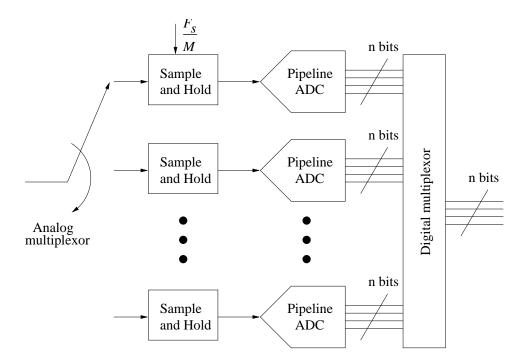

| 1.1  | Time-interleaved parallel pipeline ADC structure                                           | 2  |

|------|--------------------------------------------------------------------------------------------|----|

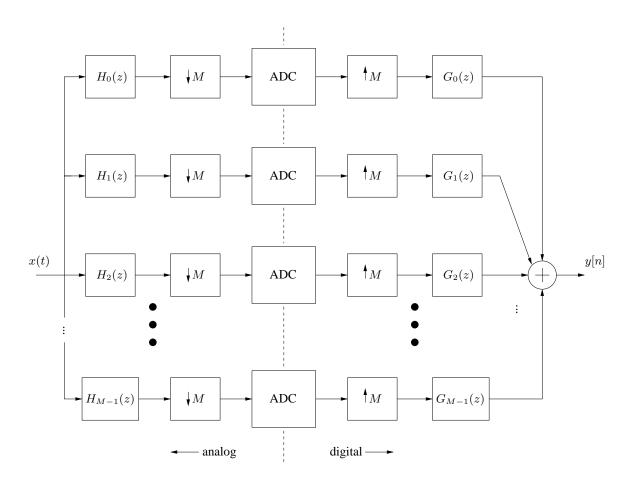

| 1.2  | M-channel frequency analysis ADC structure                                                 | 4  |

| 2.1  | Frequency spectrum of a real bandpass signal                                               | 7  |

| 2.2  | Complex IQ modulation                                                                      | 10 |

| 2.3  | Lowpass representation of $X_c(f)$                                                         | 10 |

| 2.4  | Sampling of bandpass signals                                                               | 12 |

| 2.5  | Bandpass ADC IQ Structure                                                                  | 13 |

| 2.6  | $\frac{F_s}{4}$ subsampling ADC IQ structure                                               | 14 |

| 2.7  | $\frac{3F_s}{4}$ subsampling ADC IQ structure                                              | 15 |

| 2.8  | Spectrum division for subband quantization                                                 | 17 |

| 2.9  | Recombination of 2 bands with proposed architecture                                        | 19 |

| 2.10 | Recombination of 4 bands with proposed architecture                                        | 20 |

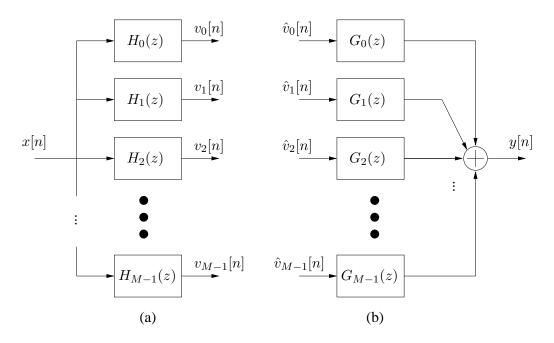

| 3.1  | (a) Analysis and (b) synthesis digital filter banks                                        | 22 |

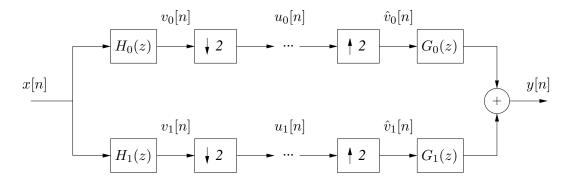

| 3.2  | 2 channel QMF bank                                                                         | 23 |

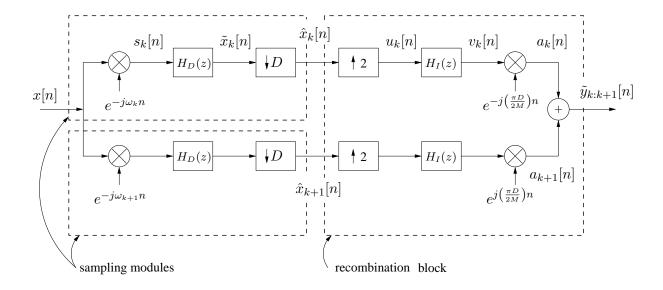

| 3.3  | Channel recombination for a 2-channel system                                               | 28 |

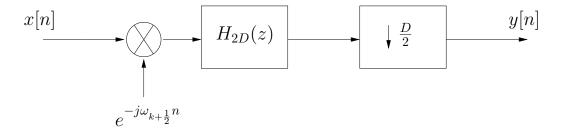

| 3.4  | Equivalent system of Figure 3.3                                                            | 29 |

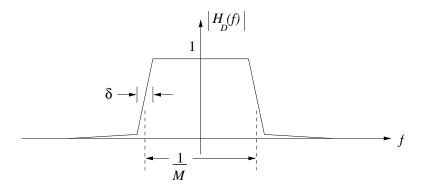

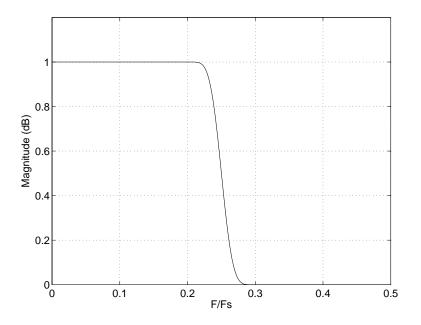

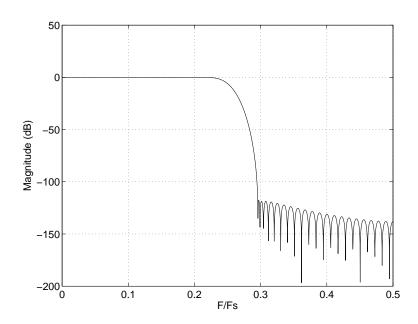

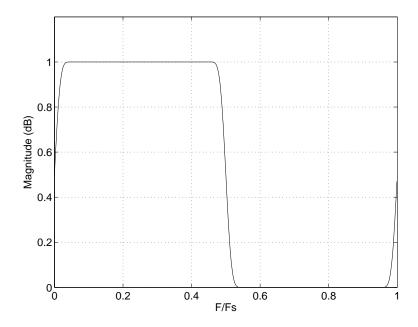

| 3.5  | Decimation filter $H_D(z)$ frequency response                                              | 31 |

| 3.6  | Terms of concern for aliasing using decimation with $D=M$                                  | 32 |

| 3.7  | Terms of concern for aliasing using decimation with $D = \frac{M}{2}$                      | 34 |

| 3.8  | Requirements for interpolation filter $H_I(z)$ frequency response (for $D = \frac{M}{2}$ ) | 38 |

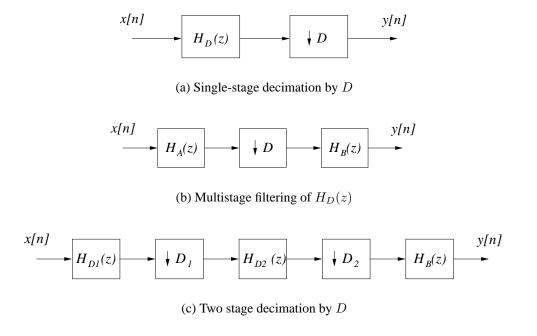

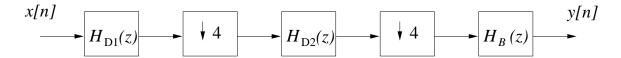

| 3.9  | Multi-stage decimation and filtering                                                       | 39 |

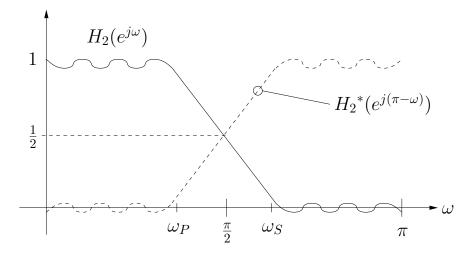

| 3.10 | Frequency response of a half-band filter                                                   | 41 |

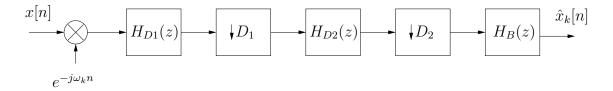

| 3.11 | Final channel decimation block design                                                      | 46 |

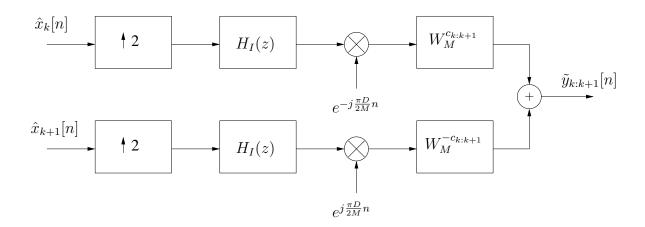

| 3.12 | Final recombination block design                                                           | 47 |

| 4.1  | Cascaded downsamplers to achieve decimation by 16                                          | 49 |

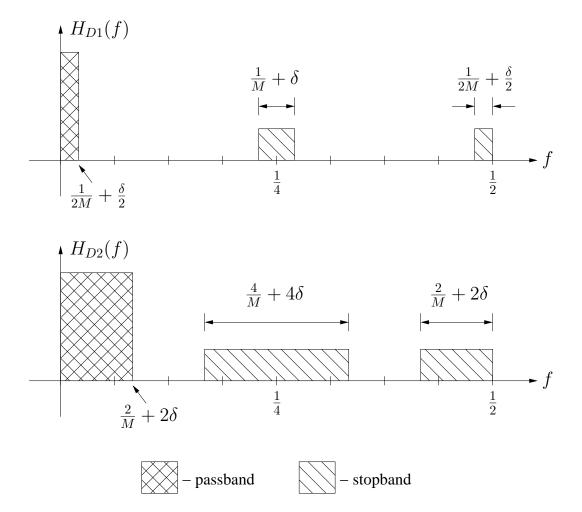

| 4.2  | Passband and stopband requirements for decimation filters $h_{D1}[n]$ and $h_{D2}[n]$              | 51 |

|------|----------------------------------------------------------------------------------------------------|----|

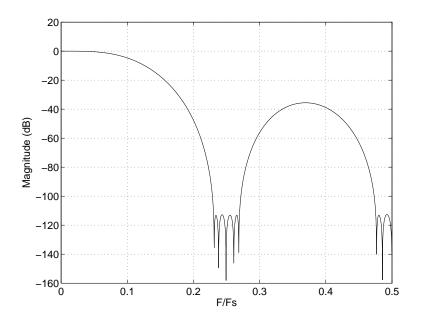

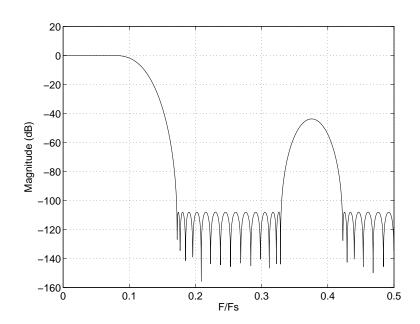

| 4.3  | Frequency responses of decimation filters                                                          |    |

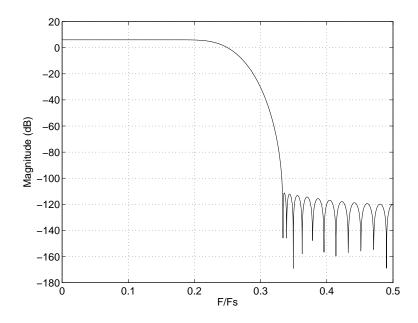

| 4.4  | Frequency response of decimation filter $h_B[n]$                                                   | 54 |

| 4.5  | Frequency response of interpolation filter $h_I[n]$                                                | 56 |

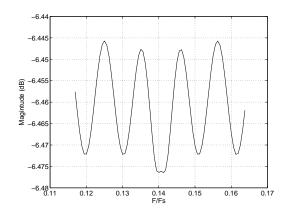

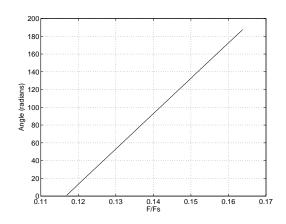

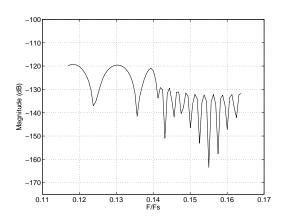

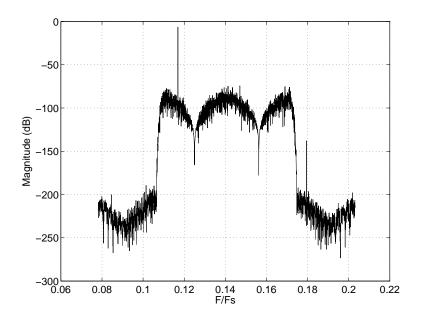

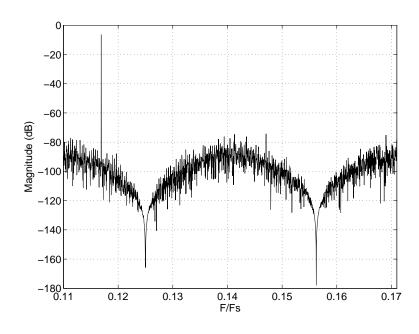

| 4.6  | Measurements for recombination of bands 4 and 5                                                    | 58 |

| 4.7  | Measurements for recombination of bands 4 through 7                                                | 60 |

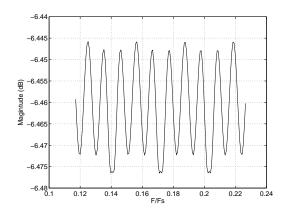

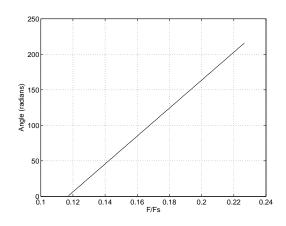

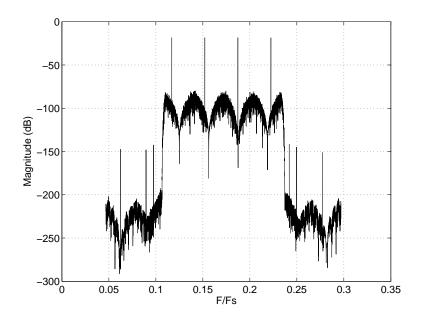

| 4.8  | Measurements for recombination of bands 0 through 15                                               | 61 |

| 4.9  | Frequency response of a Hilbert transformer                                                        | 63 |

| 4.10 | Single-tone test in bands 4 and 5                                                                  | 64 |

| 4.11 | Four-tone test in bands 4 through 7                                                                | 66 |

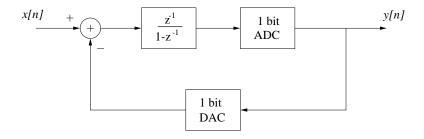

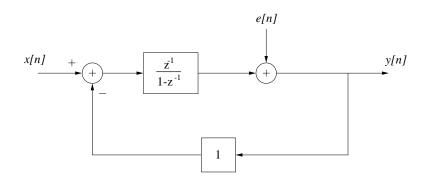

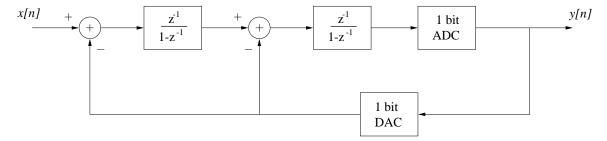

| 5.1  | Block diagram of a first order $\Sigma\Delta$ ADC                                                  | 70 |

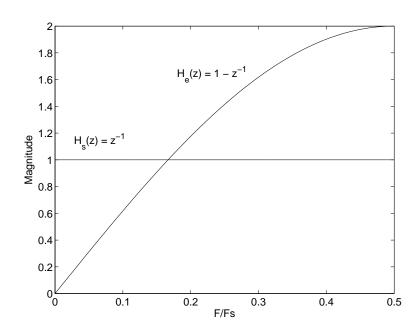

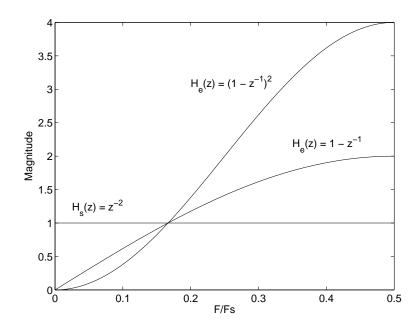

| 5.2  | Frequency response associated with the transfer functions $H_s(Z)$ and $H_e(z)$ (first order loop) | 70 |

| 5.3  | Block diagram of a second order $\Sigma\Delta$ ADC                                                 | 71 |

| 5.4  | Transfer functions $h_s[n]$ and $h_e[n]$ (first and second order loops)                            | 72 |

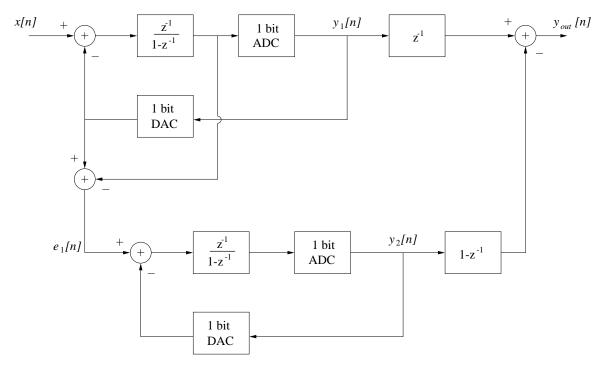

| 5.5  | $\Sigma\Delta$ MASH architecture (second order)                                                    | 72 |

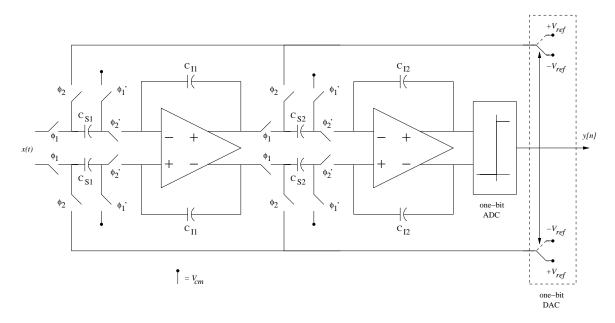

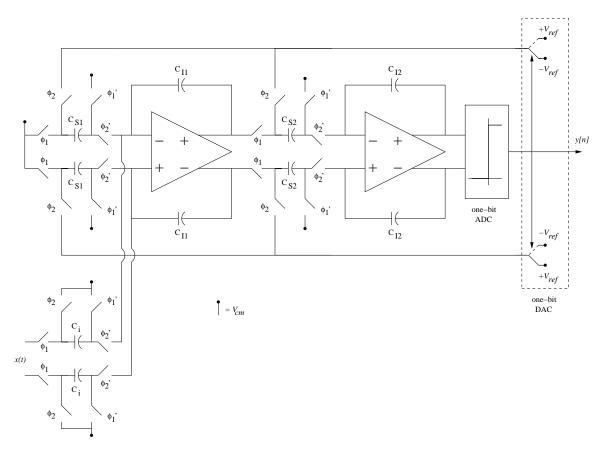

| 5.6  | Second order $\Sigma\Delta$ modulator implementation                                               | 74 |

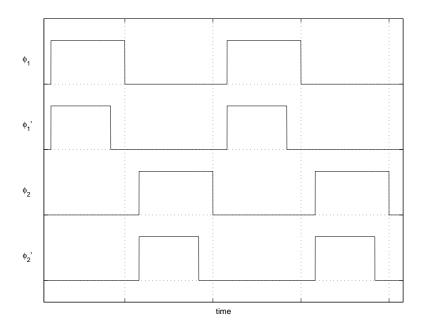

| 5.7  | Clock phases for $\Sigma\Delta$ modulator of Figure 5.6                                            | 75 |

| 5.8  | Second order $\Sigma\Delta$ loop with modulator sampling capacitors                                | 77 |

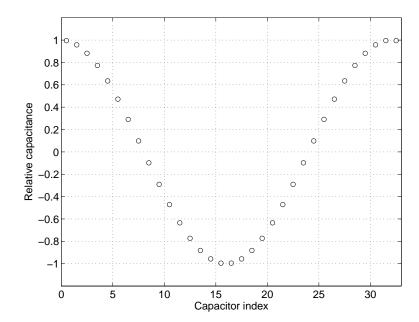

| 5.9  | Relative modulator capacitance values for OSR of 32                                                | 79 |

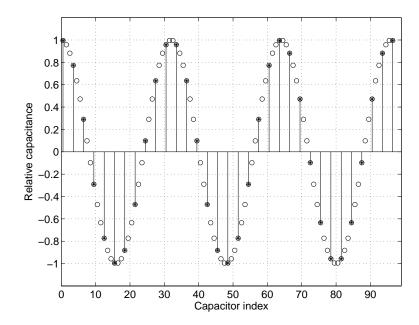

| 5.10 | Relative modulator capacitance sequence for $F_m = \frac{3F_s}{32}$                                | 80 |

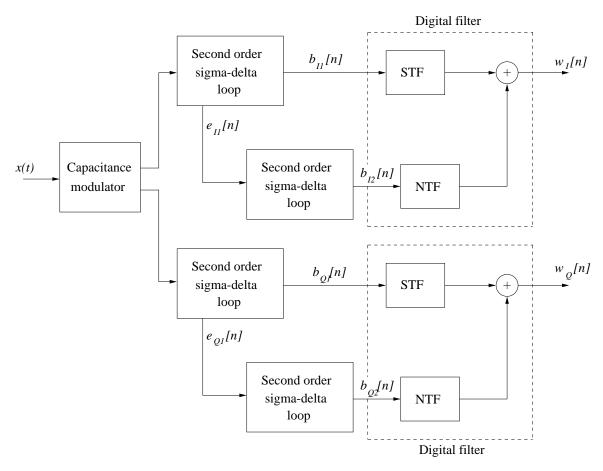

| 5.11 | Block diagram of frequency selective $\Sigma\Delta$ ADC                                            | 82 |

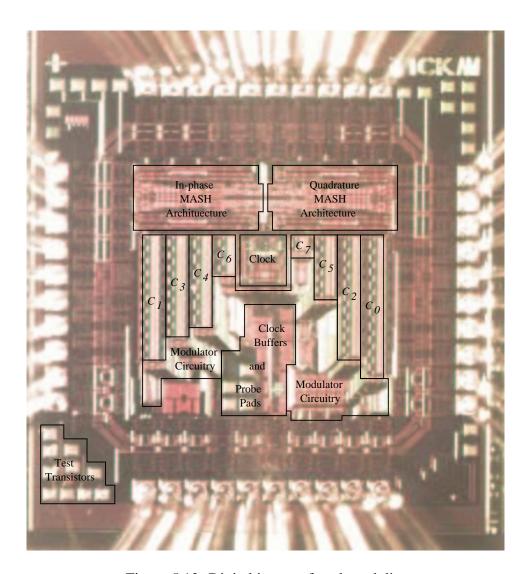

| 5.12 | Digital image of packaged die                                                                      | 83 |

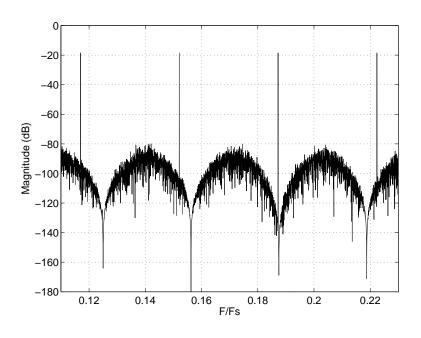

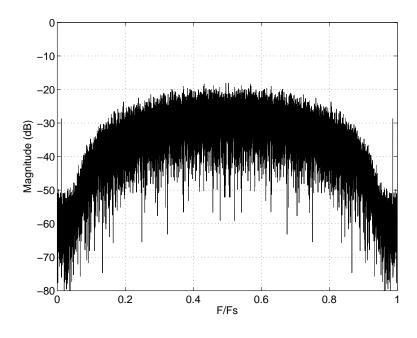

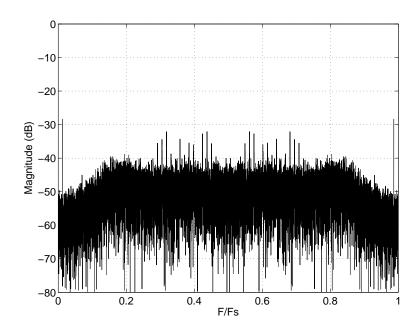

| 5.13 | Baseband test results (16 ksamples)                                                                | 85 |

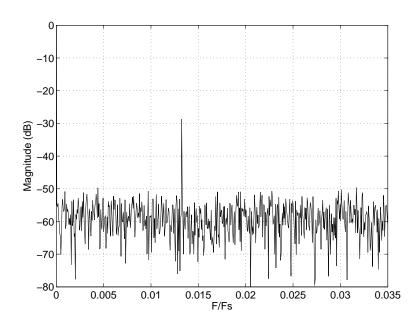

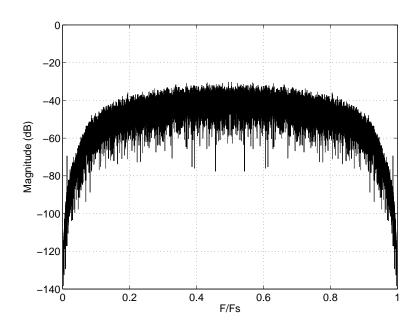

| 5.14 | Baseband test results from each stage (16 ksamples)                                                | 87 |

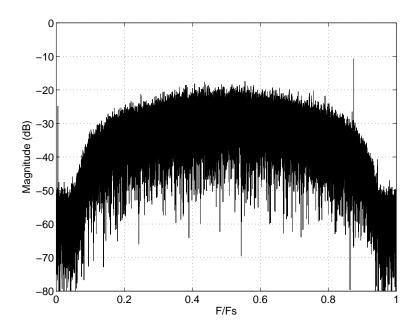

| 5.15 | Test results from $k = 4$ band (32 ksamples)                                                       | 89 |

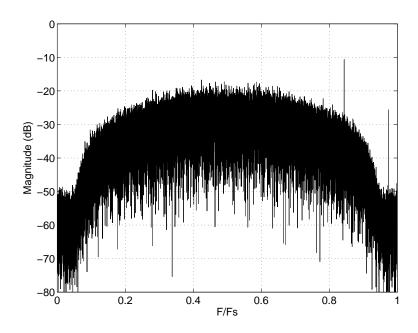

| 5 16 | Test results from $k = 5$ hand (32 ksamples)                                                       | 90 |

#### CHAPTER 1

#### INTRODUCTION

The increasing number of communications protocols and the expanding world of digital communications calls for companies to produce more versatile devices. Devices such as cellular telephones and software radios are often designed to operate using more than one method of reception to increase the number of locations in which the device may be used. At the time of this writing most cellular telephones can receive both analog and digital signals. Implementing a number of different receiver types in one device can be very expensive. There is definite need for easily implemented designs that accommodate several different communication protocols in a single device.

Many newer receiver architectures call for the signal to be digitized as early as possible. The remainder of the processing is left to lower power, reliable digital circuits more cheaply realized than their analog counterparts. In order for this to happen, the analog-to-digital converter (ADC) systems that quantize the incoming signals must become versatile and easy to implement.

Sigma-delta ( $\Sigma\Delta$ ) ADCs provide a high degree of resolution using low complexity components at a high sampling rate. The biggest drawback to using these quantizers is that the increased resolution is achieved in a very narrow band of frequencies compared to the sample rate. However, the insensitivity to circuit matching makes this converter a good candidate for multiband conversion. The outputs from multiple quantizers run in parallel can be combined to achieve the high resolution of the  $\Sigma\Delta$  ADC over a much wider bandwidth.

This thesis investigates an architecture that allows the use of a bank of  $\Sigma\Delta$  ADCs to quantize several narrow bands of frequencies. Digital filtering and sample rate conversion are then applied to approximate the perfect reconstruction of adjacent quantized bands to reproduce the wideband signal in the digital domain. Using this

Figure 1.1: Time-interleaved parallel pipeline ADC structure

architecture, a number of different frequency bands with different widths, centered at different frequencies, may be received, digitized, and subsequently processed, all by the same device. This kind of versatility can be exploited to suit several different communication protocols, with the different receiver types implemented in software all using the same hardware.

# 1.1 Background

The goal of this thesis is to implement a sampling architecture that achieves sample rates that are higher than technology allows for a single device. This can be accomplished by using multiple ADCs in parallel and interleaving their measurements in the time domain or using analysis techniques on individual bands in the frequency domain.

#### 1.1.1 Time-interleaved structure

Time-interleaved ADCs use multiple quantizers sampling at alternating intervals to increase sampling rates. Figure 1.1 shows the time-interleaved structure of parallel pipeline converters by Lin [2]. Pipeline ADCs were used because they offer high speed (greater than 10 MHz) and high resolution (10 bits or greater). Each channel samples at a rate  $\frac{F_s}{M}$ , where  $F_s$  is the sample rate of the entire structure and M is the number of channels. The sampling instant of each sample and hold block is shifted in time such that each converter takes a sequential sample in time. The outputs from each channel are collected and sequenced in digital hardware to give quantized output at a rate that is M times that of a single device.

In order for the time-interleaved structure to provide high resolution, matching between devices is of great concern. Work in [2] shows that pipeline ADCs are best suited for use in the time-interleaved structure, as they provide a high sample rate with an efficient use of chip area for a given technology. The converters used in this architecture must be wideband devices for this structure to achieve higher sampling rates. The  $\Sigma\Delta$  is therefore not a good choice for the time-interleaved structure.

## 1.1.2 Frequency analysis structure

An alternative to the time-interleaved structure is one that uses a bank of ADCs in parallel to operate on separate frequency bands in what is referred to as a frequency analysis structure. The range of input frequencies is broken into a set of subband signals for analysis. A block diagram of the basic structure appears in Figure 1.2. All the ADCs in the structure are identical devices that operate on different subband signals. The filters  $H_k(z)$  are the analog decomposition filters, and the filters  $G_k(z)$  are the digital recombination filters. Because there is no modulation of signals to lower frequencies, the need for high-speed, high-precision sample-and-hold circuitry still exists [3]. Researchers

Figure 1.2: M-channel frequency analysis ADC structure

have argued that using identical quantizers in each channel offers a more flexible architecture.

## 1.1.3 $\Sigma\Delta$ ADCs used for channel quantizers

$\Sigma\Delta$  ADCs are able to quantize signals with a high degree of resolution, provided the signal energy is located at low frequencies compared to the sample rate. Using an integrating feedback loop, this converter applies a delay to the signal input and a noise shaping transfer function to the quantization noise. Signals that reside outside the narrow baseband region that is quantized with high resolution are pushed into the quantization noise that is shaped away from baseband. Using a one-bit quantizer and a one-bit digital-to-analog converter (DAC),  $\Sigma\Delta$  ADCs are capable of achieving greater than 16-bits of resolution [4].

The  $\Sigma\Delta$  ADC has been previously employed in a multiband scheme that used one lowpass converter and several bandpass devices [5]. A high degree of resolution was achieved across a bandwidth quantized by four devices. This work supports the idea that the  $\Sigma\Delta$  ADC is a strong candidate for the quantizer used in each channel of the proposed structure due to the high resolution achieved by the converter. It is well suited to Very Large Scale Integration (VLSI) technology as it uses circuits that do not have to be well matched to produce high precision outputs.

## 1.2 Purpose of the research

The purpose of this research is to formulate an architecture that makes use of identical quantizers operating in parallel to efficiently perform wideband conversion. Each channel in the architecture contains identical hardware, so the cost of additional bandwidth is additional channels. The desired result is a structure that is able to recombine a number of smaller bandwidth signals into one with larger bandwidth. The recombined signal should have as little magnitude and phase distortion as possible across the total

recombined bandwidth, including where the edges of the smaller bands meet. The main focus of this thesis is the digital processing that allows the resolution of these parallel devices to be reliably extended to cover the first Nyquist band, which is half of the sample rate.

## 1.3 Thesis organization

Chapter 2 looks at bandpass signals and the quantization of those signals. The complex representation of bandpass signals is explained as well as the notation used throughout the remaining chapters to denote these signals. Different methods of sampling bandpass signals are discussed. Chapter 3 discusses the use of digital filter banks and their design. Multirate systems are discussed and an overview of the design of the proposed stucture is given. Chapter 4 gives an example of a filter bank designed specifically for the  $\Sigma\Delta$  modulator designed for this project [1]. The performance of the recombination filter bank is examined. In support of this work, a monolithic frequency selective IQ  $\Sigma\Delta$  modulator was designed and fabricated in a 0.5  $\mu$ m CMOS process from AMI Semiconductor. This device is the prototype for the lowpass  $\Sigma\Delta$  ADC unit used to quantize each band that is recombined digitally. Chapter 5 briefly examines the IC fabricated specifically for the architecture described in this thesis. The methods and results of the testing of the fabricated device are explained. Chapter 6 draws conclusions about the work presented in this thesis, and proposes ideas for future work.

#### **CHAPTER 2**

#### **BANDPASS SIGNALS**

This chapter provides an overview of bandpass signal quantization. The complex representation of bandpass signals is discussed in order to develop notation for later chapters and to provide insight on how bandpass signals are quantized. Different methods of sampling bandpass signals are discussed, and finally an outline of the proposed wideband ADC architecture is given.

## 2.1 Complex representation of bandpass signals

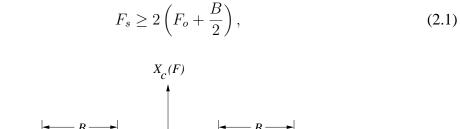

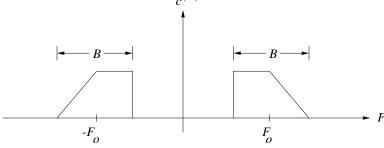

A frequency spectrum  $X_c(F)$  of a real, continuous time bandpass signal,  $x_c(t)$ , is illustrated in Figure 2.1. A real signal with energy centered at frequency  $F_o$  also has energy at the conjugate frequency,  $-F_o$ . According to the Nyquist sampling theorem, a signal must be sampled at a rate that is at least twice the maximum frequency of the signal in order to quantize the signal without losing any information [6]. For a signal centered at frequency  $F_o$  with bandwidth B, the sample rate must be

Figure 2.1: Frequency spectrum of a real bandpass signal

which may be difficult to acheive for large  $F_o$  or B. All of the information needed to accurately represent  $x_c(t)$  is contained in the positive frequencies centered at  $F_o$ , while the information contained in the negative frequencies centered at  $F_o$  is a conjugate copy of that information. Since there is no need to retain both halves of the signal spectrum, one half of the energy shown (centered at either  $F_o$  or  $F_o$ ) is enough to represent the signal, and the remaining half is redundant and can be ignored. Translation of the spectrum to the origin and lowpass filtering allows  $F_o$  to be represented at a much lower sampling rate. The highest frequency of interest is now  $F_o$  and the sampling rate must be at least twice this amount or

$$F_s \ge 2\left(\frac{B}{2}\right) = B. \tag{2.2}$$

This rate is usually considerably lower than the previous sampling rate and allows for more efficient processing of the signal. The corresponding lowpass signal, denoted  $\tilde{x_c}(t)$ , is given by

$$\tilde{x}_c(t) = L.P.P.\{x_c(t)e^{-j2\pi F_o t}\}$$

(2.3)

where  $\tilde{x}_c(t)$  is the "lowpass part" of the translated signal. The signal  $\tilde{x}_c(t)$  is complex valued and is generated by lowpass filtering a complex modulated signal.

## 2.1.1 Complex modulation

Translation of the frequency spectrum in the manner described above is acheived by complex modulation (also known as vector modulation). Euler's identity below gives the relations that are used to generate the translated signal.

$$\cos(\theta) = \frac{e^{j\theta} + e^{-j\theta}}{2}$$

$$\sin(\theta) = \frac{e^{j\theta} - e^{-j\theta}}{2j}$$

(2.4)

Combining the cosine and sine waves allows separation of the complex exponential terms in (2.4). This separates the signal into its in-phase and quadrature parts, so named because the two terms have a 90 degree phase difference and thus are in quadrature with respect to each other. Either exponential term can be extracted using a combination of cosine and sine wave signals:

$$\cos(2\pi F_c t) + j\sin(2\pi F_c t) = e^{j2\pi F_c t}$$

$$\cos(2\pi F_c t) - j\sin(2\pi f_c t) = e^{-j2\pi F_c t}.$$

(2.5)

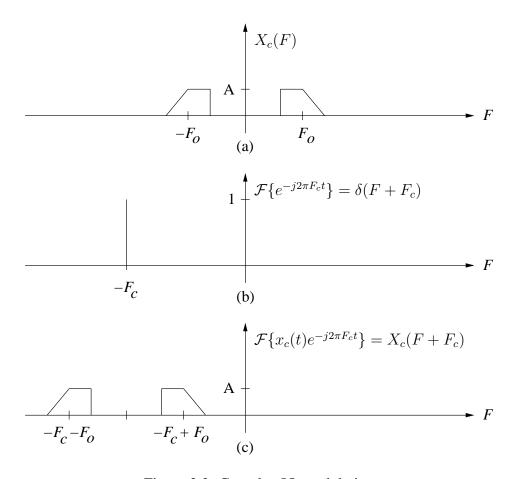

Modulation of  $x_c(t)$  with either of the complex sums shown in (2.5) yields a shift of the entire spectrum of  $x_c(t)$  in just one direction because only one of the complex exponential terms are present in the modulation. This method eliminates the possibility of aliasing terms onto each other and allows the bandpass signal centered at  $F_o$  to be mixed all the way down to the origin. The concept of complex modulation using the separated exponentials is illustrated in Figure 2.2. The frequency spectrum  $X_c(F)$  appears in Figure 2.2a. The complex exponential that modulates  $x_c(t)$  has energy only at the frequency  $-F_c$  and none at the conjugate frequency  $F_c$  as shown in Figure 2.2b. When the two spectrums are convolved, as shown in Figure 2.2c, the resulting signal is complex valued in the time domain since the resulting spectrum is no longer symmetrical about the origin. The spectrum  $X_c(F)$  has been shifted in only one direction, towards  $F = -\infty$ , using the second complex sum from (2.5). (Note that using the first complex sum would simply result in the output spectrum shifted in the opposite direction, towards  $F = +\infty$ .)

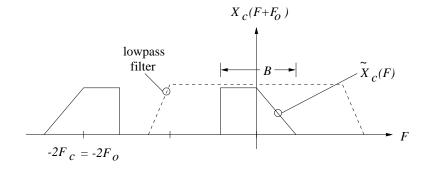

The lowpass signal  $\tilde{x}_c(t)$  is generated from a translated version of the sequence  $x_c(t)$  using complex modulation by allowing  $F_c = F_o$ . As a result  $\tilde{x}_c(t)$  is usually complex-valued when  $x_c(t)$  is real. After the translation  $\tilde{x}_c(t)$  is created by lowpass

Figure 2.2: Complex IQ modulation

Figure 2.3: Lowpass representation of  $X_c(f)$

filtering the portion of  $X_c(F)$  that now resides at the origin with bandwidth B as shown in Figure 2.3.

## 2.1.2 Properties of bandpass representations

It can be shown that the original sequence,  $x_c(t)$ , can be recovered by translating  $\tilde{x}_c(t)$  back to  $F_o$  and taking the real part of that complex-valued signal

$$x_c(t) = 2Re\{\tilde{x}_c(t)e^{j2\pi F_c t}\}.$$

(2.6)

The signal given in (2.6) can be interpreted as

$$x_c(t) = 2|\tilde{x}_c(t)|\cos(2\pi F_c t + \angle \tilde{x}_c(t))$$

(2.7)

where  $2|\tilde{x}_c(t)|$  is the envelope of the bandpass representation of  $x_c(t)$  and  $\angle \tilde{x}_c(t)$  is its phase.

The reduced bandwidth of the complex representation makes it attractive for quantizers that sample bandpass signals to produce samples of  $\tilde{x}_c(t)$  rather than  $x_c(t)$ . The sampled version of  $\tilde{x}_c(t)$  is found by evaluating the signal at discrete points in time

$$\tilde{x}[n] = \tilde{x}_c(nT_s)$$

$$= L.P.P.\{x_c(nT_s)e^{-j2\pi f_o n}\}$$

(2.8)

where

$$T_s = \frac{1}{F_s}$$

$$f_o = \frac{F_o}{F_s}.$$

(2.9)

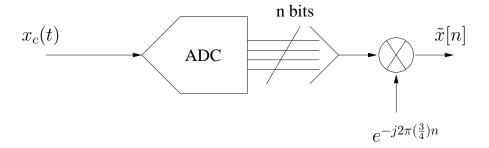

Figure 2.4: Sampling of bandpass signals

The structure shown in Figure 2.4 illustrates a bandpass sampling system as described above. The mixer and lowpass filter generate the signal  $\tilde{x}_c(t)$  and the quantizer samples the lowpass signal to produce  $\tilde{x}[n]$ . Unfortunately  $\tilde{x}[n]$  cannot be created in this manner because ADCs cannot distiguish between real and complex waveforms and are incapable of sampling complex signals by themselves. The following section discusses methods used to sample a bandpass signal using the complex respresentation of that signal.

## 2.2 Bandpass sampling schemes

Sampling bandpass signals requires a different approach than lowpass signals due to the frequency of the bandpass signal. Signals at frequencies much higher than the sampling rate of the converter may need to be sampled, which can be complicated. Several techniques for sampling high frequency bandpass signals are now discussed.

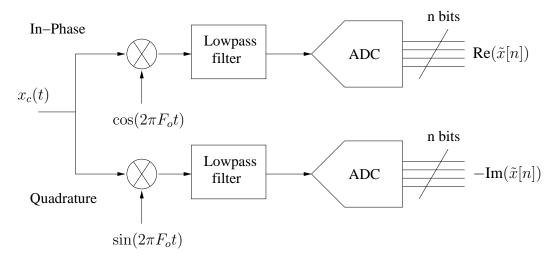

## 2.2.1 IQ ADC structure

A fairly common bandpass sampling structure is given in Figure 2.5. It consists of an "in-phase" channel and a "quadrature" channel each feeding an ADC. The modulation by cosine and sine waves generates the terms for the complex modulation that shifts the spectrum down to the origin as explained in Section 2.1.1. The in-phase channel

Figure 2.5: Bandpass ADC IQ Structure

contains all the real bits of the output, while the quadrature channel contains all the imaginary bits. The complex signal can be obtained by adding the real portion with a phase-shifted version of the imaginary portion.

$$\tilde{x}[n] = \text{Re}(\tilde{x}[n]) + j\text{Im}(\tilde{x}[n]) \tag{2.10}$$

Matching between the in-phase and quadrature channels is of great importance, as deviation from 90 degrees in the difference between the two channels can result in unwanted image frequencies. Gain mismatch between the two local oscillators can cause large tones at DC and  $\frac{f_s}{2}$  that may couple with the input signal and induce unwanted image frequencies. Analysis of both problems has been previously investigated [7]. These problems can arise as the result of analog circuitry imperfections in implementations of the in-phase and quadrature mixers.

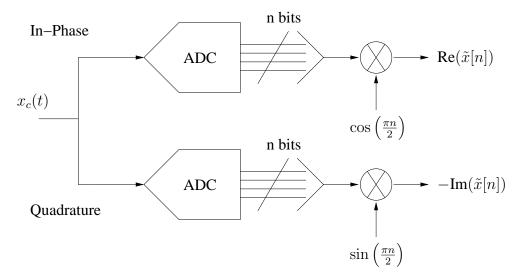

# 2.2.2 Subsampling IQ structure

One solution to reduce the sensitivity of demodulation to analog modulators in the IQ structure is to perform the multiplication in the digital domain after sampling.

Figure 2.6:  $\frac{F_s}{4}$  subsampling ADC IQ structure

This presents a problem when sampling high frequency signals, as the data rate must be increased accordingly. This technique, illustrated in Figure 2.6, makes use of subsampling in order to represent the bandpass signal at a lower frequency. When an analog signal is sampled, it is in effect multiplied by a sequence of delta functions, which causes the frequency spectrum of the sampled signal to be repeated at a period equal to the sample rate,  $F_s$ . A signal with energy at a frequency that is an integer multiple of  $F_s$  will therefore show energy at DC when sampled. By subsampling the bandpass signal, it can be quantized by a converter operating at a data rate much slower than the maximum frequency of interest in the signal. The technique of subsampling is used to perform most of the frequency translation on the bandpass signal, as mixing it all the way down to baseband would cause aliasing of the signal.

Once the signal has been quantized, complex modulation is used to mix the signal down to DC as in the IQ structure. As described below, a popular choice is to select the sample rate so that the bandpass signal is aliased onto a bandwidth centered at  $\frac{F_s}{4}$ . At this point complex modulation is performed in the digital domain, which can be done more reliably than with analog multipliers. The signal needs to be translated by  $\frac{F_s}{4}$  which corresponds to multiplying the sequence by the complex exponential  $e^{-j2\pi(\frac{1}{4})n}$

Figure 2.7:  $\frac{3F_s}{4}$  subsampling ADC IQ structure

which can be accomplished by using cosine and sine modulation in each channel:

$$\cos\left(\frac{\pi}{2}n\right) - j\sin\left(\frac{\pi}{2}n\right) = e^{-j\frac{\pi}{2}n}.$$

(2.11)

The frequency  $\frac{F_s}{4}$  is chosen because the modulating signals are easily generated. The signals are simply a stream of three values as shown below.

$$\cos\left(\frac{\pi}{2}n\right) = 1, 0, -1, 0, 1, 0, -1, 0, \dots$$

$$\sin\left(\frac{\pi}{2}n\right) = 0, 1, 0, -1, 0, 1, 0, -1, \dots$$

(2.12)

The use of ones and zeros eliminates the need to store any filter coefficients in memory.

Due to the non-overlapping nature of the cosine and sine wave streams in (2.12), they can be combined into one digital stream consisting of

$$e^{-j2\pi(\frac{3}{4})n} = 1, j, -1, -j, 1, j, -1, -j, \dots$$

(2.13)

By sampling the bandpass signal so that it is centered at  $\frac{3F_s}{4}$ , only one channel is needed because the complex modulation is performed digitally. One quantizer can produce the samples at a reduced rate using half as much hardware as needed for the  $\frac{F_s}{4}$  subsampling architecture. The simplified structure appears in Figure 2.7.

At this point there are a few issues that should be considered using this toplogy in a multimode receiver. The input of the structure requires filtering to insure that nothing in any of the lower bands aliases into the signal during sampling. This filter is normally bandpass and attenuates everything but the desired signal band, which may be difficult at higher frequencies. For converting many bands, each ADC must operate at a different data rate, meaning the converters may not be the same in each channel.

## 2.2.3 $\Sigma\Delta$ bandpass sampling

Bandpass versions of the  $\Sigma\Delta$  converter have been developed that can quantize a bandpass signal with high resolution, as it shapes quantization noise away from a particular center frequency. These converters acheive a bandwidth of high resolution that is limited to a small fraction of the sample rate, similar to that of the lowpass converter [8].

$\Sigma\Delta$  converters use low complexity circuits easily realized in VLSI technology to quantize signals with a high degree of resolution. They operate by sampling a signal at a rate that is many times higher than the bandwidth of the signal, which makes it an oversampled converter. An integrating feedback loop is used to average the samples taken by a one-bit quantizer to provide appropriate noise shaping in order to obtain a high resolution output. The oversampling spreads quantization error over a larger range of frequencies than critically sampled converters, and the integration and feedback push noise away from DC in what is called "noise shaping." By altering the loop transfer function of a lowpass  $\Sigma\Delta$  converter, a quantizer that provides noise shaping at a frequency other than DC can be constructed. These bandpass  $\Sigma\Delta$  converters provide high resolution for a band of frequencies that is much smaller than the data rate.

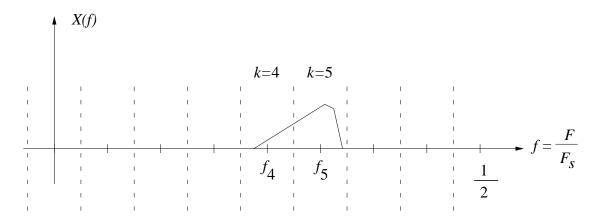

Figure 2.8: Spectrum division for subband quantization

## **2.2.4** $\Sigma\Delta$ **IQ** structure

The particular architecture implemented in this thesis uses  $\Sigma\Delta$  ADCs in an IQ structure. Different parts of the signal are modulated down to baseband where they are quantized by the ADCs in the in-phase and quadrature channels. The output of the structure is the complex representation of a bandpass signal quantized with the resolution of the  $\Sigma\Delta$  converter. This structure can only quantize narrow bandwidth signals, much like the bandpass  $\Sigma\Delta$ . The frequency band that this structure operates on is variable, unlike the bandpass unit which operates on a fixed center frequency. Work done in [1] shows that the mixers in Figure 2.5 can be implemented in the front-end of a switched-capacitor  $\Sigma\Delta$  ADC as will be explained in Chapter 5.

# 2.3 Proposed structure

In order to quantize a signal with wide bandwidth, it is necessary to use multiple ADCs running in parallel to quantize the signal. This system follows the frequency analysis approach to wideband quantization by dividing the input frequency range into a number of bands. The spectrum can be divided into M bands, each with bandwidth

equal to  $\frac{F_s}{M}$ . The band centers are given by

$$F_k = \frac{F_s k}{M}$$

$k = 0, 1, 2, \dots \frac{M}{2} - 1$  (2.14)

where only the first  $\frac{M}{2}$  bands are converted due to the fact that the second Nyquist band contains redundant information once the signal has been sampled. The division of the frequency spectrum is illustrated in Figure 2.8, where the spectrum of the quantized signal, x[n], has energy located in two different bands. Each band is processed by a separate channel containing the bandpass sampling modules. In each sampling module, the signal is demodulated in order to allow the quantizer in that channel to operate on a lowpass signal. The same type of converter can therefore be used to quantize different parts of the signal while operating at the same sample rate.

The  $\Sigma\Delta$  IQ ADC structure is employed to sample each bandpass section of the full signal. This method requires two ADC devices per channel for creating the in-phase and quadrature samples. The channels should be divided such that each channel is no larger than the bandwidth of the lowpass  $\Sigma\Delta$  ADC which, due to the noise shaping, is normally considered to be

$$B_{\Sigma\Delta} = \frac{1}{2\text{OSR}} \tag{2.15}$$

where OSR is the over-sampling rate of the converter. The obvious choice for the channel width is to set the number of channels, M, equal to the over-sampling rate, meaning that the ADC conversion bandwidth and the channel bandwidth are the same.

The filtering in each channel provides a means for selecting each bandpass part of the signal that will be recombined. It also serves to prevent aliasing of the signal when the signal is decimated. The most important consideration in the design of the filter banks is that the pieces of the original signal are recombined without causing any distortion at the edges of the bands. Adjacent signal bands must be filtered such that the edges add to reconstruct the information properly.

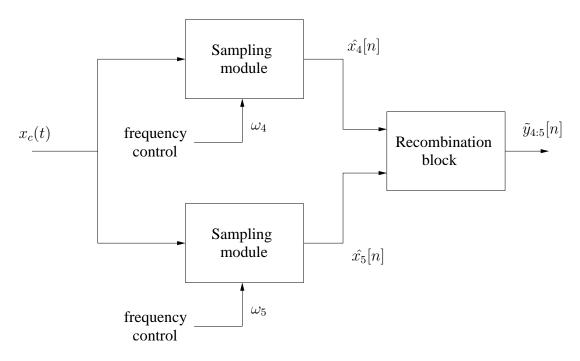

Figure 2.9: Recombination of 2 bands with proposed architecture

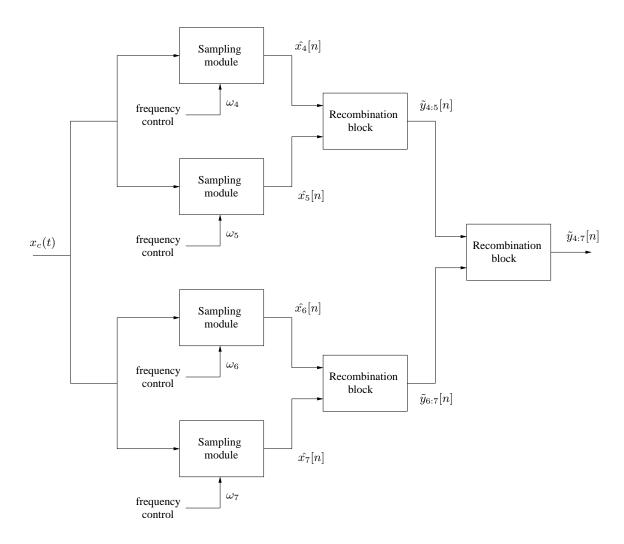

Figure 2.9 shows two channels of the M-channel structure. The signals  $\hat{x}_4[n]$  and  $\hat{x}_5[n]$  are decimated versions of the complex subband signals  $\tilde{x}_4[n]$  and  $\tilde{x}_5[n]$ , respectively. The sampling module operates on a particular bandwidth of the signal centered at  $\omega_k$  in order to produce samples of  $\tilde{x}_k[n]$ . The sampling module translates the signal band to baseband before quantization, and then decimates it in preparation for the recombination block. The signal  $\tilde{y}_{k:k+1}[n]$  is the recombined output of channels k through k+1, where the subscript k:k+1 is used to denote the channels that the recombined output spans. The signal  $\tilde{y}_{4:5}[n]$  can then be recombined with the signal  $\tilde{y}_{6:7}[n]$  from the adjacent recombination block in order to create the signal  $\tilde{y}_{4:7}[n]$  as shown in Figure 2.10. These blocks are simply cascaded in a tree structure to recombine additional bands.

Figure 2.10: Recombination of 4 bands with proposed architecture

#### CHAPTER 3

#### **FILTERING**

This chapter discusses digital filter banks and their applications in digital signal processing. A few different architectures are discussed, and important design aspects for a filter bank that performs the recombination for this application are given.

## 3.1 Digital filter banks

Filter banks are important tools in digital signal processing that allow signals to be separated into their smaller parts for simpler processing, often at a reduced data rate. A digital filter bank normally consists of a set of bandpass filters processing a common input signal or feeding a summed output. The bandpass filters usually pass non-overlapping signal bands.

Filter banks are primarily broken into two catagories, which are analysis filter banks and synthesis filter banks. An analysis filter bank, shown in Figure 3.1a, takes one signal and filters it into several smaller bandwidth signals. Figure 3.1b shows a synthesis filter bank which performs the opposite function of combining a set of subband signals into one. Usually the emphasis in the design of a filter bank is on the quality of the separation or recombination. A system which does not distort the magnitude of the signal is said to be "magnitude preserving." Such a system may scale the amplitude of the input signal. Most systems apply a sample delay to the input signal, as a finite amount of time is required to process the signal. A system that does not produce phase distortion or add a linear term to the phase of the signal is called "phase preserving." A system that preserves both the magnitude and phase characteristics of the input signal is said to "perfectly reconstruct" the input signal. A perfect reconstruction system has a transfer function that resembles

$$H(z) = az^{-d} (3.1)$$

Figure 3.1: (a) Analysis and (b) synthesis digital filter banks

where a is an amplitude scaling factor and d is an integer sample delay. The output of such a system is a scaled, delayed version of the input.

#### 3.1.1 Uniform DFT filter banks

Uniform DFT filter banks are constructed from a single lowpass prototype filter with real coefficients. The frequency response of the prototype filter is then translated in frequency to M uniformly spaced points across the frequency spectrum from DC (k=0) to just below  $f_s$  (k=M-1). This is accomplished through complex modulation using the exponential

$$e^{-j\frac{2\pi}{M}kn} = W_M^{kn} \tag{3.2}$$

where the commonly used notation

$$W_{\lambda} = e^{-j\frac{2\pi}{\lambda}} \tag{3.3}$$

Figure 3.2: 2 channel QMF bank

has been used. The resulting filters (other than k=0) all have complex coefficients and equal passband widths of  $\frac{F_s}{M}$ . The input signal is then processed by these filters in parallel which disects the signal into M bands for analysis. These filters are easily designed and implemented, since only one filter must be designed. This filter is a lowpass filter with bandwidth  $\frac{F_s}{2M}$ .

In a variation of the uniform DFT filter bank, the same lowpass prototype filter is again designed. Instead of translating the frequency characteristic of the filter to select different bands, the input signal is translated so that the band of interest for each channel falls in the passband of the lowpass filter. The analysis filter bank consists of M copies (where M is the number of channels) of the lowpass prototype filter and the complex mixers that proceed the filters, each using a different local oscillator frequency

$$\omega_k = \frac{2\pi F_k}{F_s}$$

$$= \frac{2\pi k}{M} \qquad k = 0, 1, 2, \dots M - 1.$$

(3.4)

The synthesis filter bank for this architecture also requires complex mixers in order to shift the pieces of the input signal back to their original postitions.

## 3.1.2 Quadrature mirror filter banks

A 2 channel quadrature mirror filter (QMF) bank, shown in Figure 3.2, is an example of a multirate system [6]. The signal is processed at different rates throughout the system in order to acheive more efficient processing. This family of filter banks is so named because of the frequency response of the filters that comprise them. For the most basic two-channel version, the filters are symmetric about the quadrature frequency of  $\omega = \frac{\pi}{2}$ . In the analysis filter bank, the input signal spectrum is divided in half, with the lower frequencies and the upper frequencies processed by separate channels. Because each channel only handles half of the input spectrum, the data can be coded at half the input sample rate. At this point the signals are either transmitted or further processed. When signals are received at the synthesis filter bank, the goal is to recombine data from the two channels to reconstruct the original signal. The sample rate is doubled in both channels before interpolation filters select portions of each channel for recombination. These filters must prepare the two halves of the spectrum to be recombined at the original sample rate.

The equations that guide the design of the QMF bank are easily obtained through z-transform analysis of the signals at various points in the channels [6]. For the purpose of this analysis it is assumed that the signal does not undergo any processing between the analysis and synthesis banks. The signal is first filtered into a highpass and a lowpass signal in each channel

$$V_k(z) = H_k(z)X(z) \tag{3.5}$$

where k is either 0 or 1 to designate the channel that passes DC or high frequency respectively. The signal is now divided between the two channels, with each channel processing half of the original signal. In order to achieve more efficient coding, the signals are decimated by a factor of 2. The down-sampling relation for decimation by a

factor L in the z-domain is

$$X_D(z) = \frac{1}{L} \sum_{l=0}^{L-1} X(z^{1/L} W_L^{-l}).$$

(3.6)

The downsampled signal in one channel is then found to be

$$U_k(z) = \frac{1}{2} [V_k(z^{1/2}) + V_k(-z^{1/2})]$$

$$= \frac{1}{2} [H_k(z^{1/2})X(z^{1/2}) + H_k(-z^{1/2})X(-z^{1/2})].$$

(3.7)

The downsampling introduces a certain amount of aliasing of the signals in each channel depending on the filters  $H_0(z)$  and  $H_1(z)$ . This aliasing makes simple recombination of the signals difficult, and the filters  $G_0(z)$  and  $G_1(z)$  must be designed to cancel out the aliasing terms upon recombination. The upsampling relation for interpolation by a factor L is given by

$$X_U(z) = X(z^L). (3.8)$$

After the sample rate is doubled in the synthesis bank, the signals are given by

$$\hat{V}_{k}(z) = U_{k}(z^{2})$$

$$= \frac{1}{2} [H_{k}(z)X(z) + H_{k}(-z)X_{k}(-z)].$$

(3.9)

The recombined signal Y(z) is the sum of the filtered outputs from both channels

$$Y(z) = \hat{V}_0(z) + \hat{V}_1(z)$$

$$= \frac{1}{2} [H_0(z)G_0(z) + H_1(z)G_1(z)]X(z)$$

$$+ \frac{1}{2} [H_0(-z)G_0(z) + H_1(-z)G_1(z)]X(-z).$$

(3.10)

The relation in (3.10) is separated into two terms

$$Y(z) = T(z)X(z) + A(z)X(-z)$$

(3.11)

where the first term is the desired output of the system, and the second term is unwanted distortion. The signal X(z) occupies the entire bandwidth, and the addition of X(-z) represents aliased information in the signal. The goal is to design the filters  $H_k(z)$  and  $G_k(z)$  such that

$$A(z) = 0. (3.12)$$

An alias-free realization of the two-channel QMF structure can be designed by choosing

$$H_1(z) = H_0(-z)$$

$G_0(z) = H_0(z)$

$G_1(z) = -H_1(z) = -H_0(-z)$  (3.13)

which meets the requirement of (3.12). The solution is then reduced to designing the filters  $H_0(z)$  and  $H_1(z)$  such that

$$|H_0(z)|^2 + |H_1(z)|^2 = 1.$$

(3.14)

Filters  $H_0(z)$  and  $H_1(z)$  are said to be power complimentary when (3.14) is satisfied. Filter banks using linear phase filters, with responses as given in (3.14), are perfect reconstruction filter banks [6].

The degree to which the output of the QMF bank resembles the input determines the recombination performance. Much emphasis has been placed on the design of linear phase perfect reconstruction filter banks (LPPRFBs). Straightforward analysis is only

able to produce a trivial case for which linear phase filters can be designed to satisfy the perfect reconstruction requirements. In order to find more solutions, one of the requirements is relaxed and optimization routines can find close solutions. Usually the magnitude preserving requirement of (3.14) is relaxed and linear phase filters are used as in [9]. Filter coefficients are then iteratively adjusted to provide as little distortion at the band edges as possible.

The theory behind QMF banks has been extended beyond the two-channel case to include M-channel structures. These are well suited to the recombination of several bands of digitized signals. A similar approach to the M-channel case is taken in the design of the proposed structure.

## 3.2 Multirate filter bank for signal reconstruction

The filter bank structure in this design is modeled after the QMF bank structure given in Section 3.1.2. Each channel is decimated to allow more efficient processing of the signal in later stages, and the filter design is governed by the transfer function of the recombined signal. The major difference between this design and the QMF bank is that the QMF bank is almost always optimized for reassembling a predetermined number of channels (which is usually the same number of channels that were separated in the system). The degree to which the signal is reconstructed depends on the frequency responses of all of the filters in the bank. The QMF bank does not perform as well if any of the channels are left out of the recombination. The design proposed in Section 2.3 allows the user to determine the number of recombined channels based on the needs of the receiver. The only limit to the number of recombined channels is that it needs to be a multiple of two, as the system recombines two adjacent bands at every stage regardless of the size of the bands. These bands double in size at every stage, so the system has a tree-like structure.

Figure 3.3: Channel recombination for a 2-channel system

The basic 2-channel structure that allows digital recombination of a wideband signal from its subband quantized parts is shown in Figure 3.3. The structure is the realization of that in Figure 2.9 used to recombine two adjacent channels. Additional channels are recombined through repeated stages of the recombination block. The demodulation and decimation at the front of the channel prepare the signal for the recombination stage. This implementation uses linear phase filters to preserve the phase information of the signal. Magnitude distortion is minimized by matching the transition edges of the filters of adjacent channels together, so the only distortion comes from passband ripple.

### 3.2.1 Band demodulation

The demodulation step selects the particular band that will be processed by each channel. As discussed in Section 2.1.1, complex modulation is used to obtain the lowpass complex representation of the subband signal. The entire signal is processed through in-phase and quadrature channels where it is multiplied by the complex exponential from (3.2) with the superscript k indicating which band the channel will operate on as

Figure 3.4: Equivalent system of Figure 3.3

in (2.14). Each channel needs two quantizers and two mixers to create the samples, although it should be noted that the two channels for in-phase and quadrature signal generation are different than the channels that recombine two adjacent parts of the signal.

The best way to implement the demodulation step is to perform the multiplication after the signal has been digitized. "Pre-sampling" the signal using a sample-and-hold (S/H) circuit, with different capacitor values, allows a digital multiplication of the signal before it reaches the quantizer. Performing the frequency translation inside the ADC may also be an option, depending on the converter topology chosen. In Figure 3.3 it is assumed that the signal has been quantized before the filter bank is applied for the purposes of the following analysis.

# 3.2.2 Filtering and sample rate conversion

The process of filtering the bandpass signals in the system is performed at several different sample rates. The filters  $H_D(z)$  and  $H_I(z)$  serve two purposes. They prevent aliasing during decimation and filter out redundant information after interpolation. They must be designed so that neighboring bands can be recombined without causing any distortion at the band edges. If the system is able to recombine two channels without distorting either subband signal, then the composite system should be equivalent to the

system of Figure 3.4, where the filter  $H_{2D}(z)$  has a bandwidth that is twice that of filter  $H_D(z)$ .

The analysis of the two channel recombination filter bank follows very closely to that of the QMF bank. The intermediate signals along the path of each channel in Figure 3.3 are now examined. For a system consisting of M channels, the sampled bandwidth of each subband signal  $\hat{x_k}[n]$  is  $\frac{1}{M}$ . The shifted version of x[n], denoted  $s_k[n]$ , has z-transform

$$S_k(z) = X(ze^{j\omega_k})$$

$$= X(zW_M^{-k})$$

(3.15)

where (3.4) has been substituted for  $\omega_k$ . The signal  $\tilde{x}_k[n]$  is the complex representation of the subband signal to be recombined, which is created by the methods discussed in Section 2.1. This signal is simply a filtered version of  $s_k[n]$ , where the filter  $h_D[n]$  is designed to eliminate any terms that may alias onto the desired band after further processing. The decimation by a factor D allows the desired signal to fill most of the new sampling bandwidth which makes subsequent processing much easier in terms of filter coefficients and resolution. However, the down-sampling might also corrupt the signal if the filter  $h_D[n]$  is not designed correctly. Decimation stretches the frequency axis but, due to the nature of the sampled signal, its frequency spectrum is always periodic with period f=1. The lowpass filter  $H_D(z)$  must therefore pass the signal in the range  $|f| \leq \frac{1}{2M}$  and attenuate signals past the frequency  $f=\frac{1}{D}-\frac{1}{2M}$ . The processed bandpass signal  $\hat{x}_k[n]$  appears in the z-domain as

$$\hat{X}_{k}(z) = \frac{1}{D} \sum_{i=0}^{D-1} \tilde{X}_{k}(z^{1/D}W_{D}^{-i})$$

$$= \frac{1}{D} \sum_{i=0}^{D-1} H_{D}(z^{1/D}W_{D}^{-i})X(z^{1/D}W_{D}^{-i}W_{M}^{-i}).$$

(3.16)

Figure 3.5: Decimation filter  $H_D(z)$  frequency response

At this point it is important to note the value of the decimation rate D in relation to the number of channels M. It is allowable to have  $D \leq M$ , since the data in the channel will be preserved as long as the bandwidth after decimation and filtering is  $\leq \frac{1}{M}$ . For D > M the narrow band signal will be subject to aliasing, which will distort the signal in a manner that cannot be reversed. For the following discussion on different decimation rates it is assumed that the frequency response of the filter  $H_D(z)$  is as shown in Figure 3.5 where the finite transition bandwidth of the filter, denoted  $\delta$ , is defined.

### Case 1 - Maximally decimated filter bank

The filter bank with D=M is called maximally decimated, which means that the final decimated bandwidth is as wide as each channel, with no spare room at the edges. This can be a problem when the decimation filter has a finite transition bandwidth.

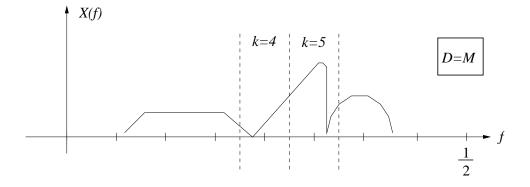

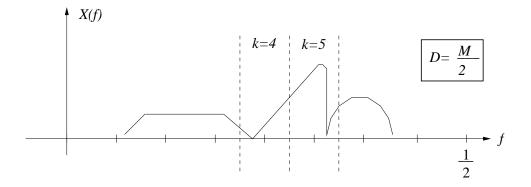

The original spectrum of the sampled signal X(f) appears in Figure 3.6(a), where the frequency bands of interest for k=4 and k=5 are noted. The adjacent signals for these particular values of k,  $\hat{X}_4(z)$  and  $\hat{X}_5(z)$ , are targeted for recombination. Due to the filter transfer function,  $H_D(z)$ , only a small band of the original signal is passed to the down-sampler in each channel. The filter  $H_I(z)$  also has a lowpass transfer function, so the i=0 term in (3.16), which is centered at DC, is the term that the

(a) Frequency spectrum of wideband signal

$$\hat{X}_4(z) = \frac{1}{D} \sum_{i=0}^{D-1} H_D(z^{1/D} W_D^{-i}) X(z^{1/D} W_D^{-(4+i)})$$

(b) Potential aliasing terms of  $\hat{X}_4(z)$

$$\hat{X}_5(z) = \frac{1}{D} \sum_{i=0}^{D-1} H_D(z^{1/D} W_D^{-i}) X(z^{1/D} W_D^{-(5+i)})$$

(c) Potential aliasing terms of  $\hat{X}_5(z)$

Figure 3.6: Terms of concern for aliasing using decimation with  $D={\cal M}$

filter bank should preserve. When the decimated signal covers the entire first Nyquist band there may be some aliasing from the adjacent terms i=1 and i=M-1 in the sum. The terms of interest in the summation for  $\hat{X}_4(z)$  and  $\hat{X}_5(z)$  are shown in Figures 3.6(b) and 3.6(c), respectively. It can be seen that for the case where D=M there is aliasing at the band edges due to these adjacent terms, where shading has been used to illustrated the areas of overlap for each term. The residue from the adjacent terms that leaks onto the i=0 term is caused by the finite transition bandwidth  $\delta$  of the filter  $H_D(z)$ . This aliasing causes distortion that cannot be undone simply by interpolation and filtering. It is for this reason that this design focuses on finding solutions for filter banks that use D < M.

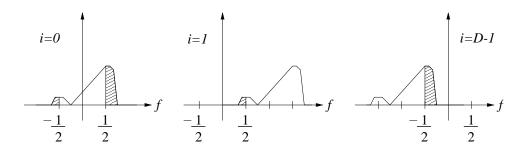

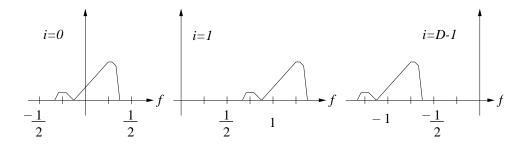

#### Case 2 - Relaxed decimation

By relaxing the decimation rate compared to the number of channels, the amount of aliasing can be significantly reduced. Leaving space between each aliased term for the overlap of the transition bandwidth of the decimation filter  $H_D(z)$  allows the interpolation filter  $H_I(z)$  to eliminate all other terms other than desired signal. After these terms have been removed, the recombination depends on lining up the edges of signals that have been filtered by  $H_D(z)$ . The filter design problem then becomes finding a good design for  $H_D(z)$ .

Figure 3.7 illustrates relaxed decimation by  $D = \frac{M}{2}$ , where the same parts of the original wideband signal, shown again in Figure 3.7(a), are to be processed. The terms in Figure 3.7(b) and 3.7(c) are still centered at the same frequencies, but now they are half as wide as before. This leaves space between the three terms, and there is no overlap between terms. The stopband attenuation of filter  $H_D(z)$  must be large enough so that any aliased terms will be negligable. The case for  $D = \frac{M}{2}$  is the largest decimation rate that can be used without causing any aliasing of the desired term.

(a) Frequency spectrum of wideband signal

$$\hat{X}_4(z) = \frac{1}{D} \sum_{i=0}^{D-1} H_D(z^{1/D} W_D^{-i}) X(z^{1/D} W_D^{-\left(\frac{4}{2}+i\right)})$$

(b) Potential aliasing terms of  $\hat{X}_4(z)$

$$\hat{X}_5(z) = \frac{1}{D} \sum_{i=0}^{D-1} H_D(z^{1/D} W_D^{-i}) X(z^{1/D} W_D^{-\left(\frac{5}{2}+i\right)})$$

(c) Potential aliasing terms of  $\hat{X}_5(z)$

Figure 3.7: Terms of concern for aliasing using decimation with  $D=\frac{M}{2}$

By using a decimation rate D < M, a linear phase filter bank can be designed that eliminates any contribution to the signal by terms other than i = 0 in (3.16). For the purpose of the analysis, the signal  $\hat{x}_k[n]$  now appears as

$$\hat{X}_k(z) = \frac{1}{D} H_D(z^{1/D}) X(z^{1/D} W_M^{-k})$$

(3.17)

provided that D < M. The requirements for the filter  $H_D(z)$  at this point are that it needs to pass signals in the range  $0 \le f \le \frac{1}{M} - \frac{\delta}{2}$ , and that it needs to provide a large amount of attenuation to signals in the range  $\frac{1}{M} + \frac{\delta}{2} \le f \le \frac{1}{2}$ . The transition band requirements will be derived once the recombination stage has been discussed.

## 3.2.3 Recombination stage

The recombination stage is designed to add together two adjacent bands of the same bandwidth. As shown in Figure 3.3, the recombination begins with an interpolation step that increases the sample rate by a factor of two. This widens the sampled bandwidth to a size that is large enough to fit the signals from both channels. The signal  $u_k[n]$  is an up-sampled version of the subband signal  $\hat{x}_k[n]$  given in the z-domain by

$$U_k(z) = \hat{X}_k(z^2)$$

$$= \frac{1}{D} H_D(z^{2/D}) X(z^{2/D} W_M^{-k}). \tag{3.18}$$

The interpolation produces another copy of the desired signal band in the sampled bandwidth, and the interpolation filter,  $H_I(z)$ , is included to remove that copy. The signal  $v_k[n]$  is the lowpass filtered version of  $u_k[n]$ , meaning that  $v_k[n]$  and the signal produced from the adjacent band,  $v_{k+1}[n]$ , each contain the lowpass versions of the subband signals for the k and k+1 bands. These signals are then complex modulated in different directions in order to construct the lowpass version of the signal bandwidth that

is twice as large as that in a single channel. The size of the frequency translation depends on the down-sampling rate. The two channels should be shifted by half the width of the signal band after the interpolation filter, which for the maximally decimated case, would be  $f=\frac{1}{4}$ . For the case of relaxed decimation, this shift is scaled by the ratio of  $\frac{D}{M}$ , yielding a shift of  $f=\frac{D}{4M}$ . The signal  $a_k[n]$  in the z-domain is found to be

$$A_{k}(z) = V_{k}(ze^{j\frac{\pi D}{2M}n})$$

$$= \frac{1}{D}H_{I}(ze^{j\frac{\pi D}{2M}})H_{D}(z^{2/D}e^{j\frac{\pi}{M}})X(z^{2/D}e^{j\frac{\pi}{M}}W_{M}^{-k})$$

$$= \frac{1}{D}H_{I}(zW_{M}^{-D/4})H_{D}(z^{2/D}W_{M}^{-1/2})X(z^{2/D}W_{M}^{-(k+\frac{1}{2})})$$

(3.19)

and the signal  $a_{k+1}[n]$  in the opposite channel is given by

$$A_{k+1}(z) = \frac{1}{D} H_I(zW_M^{D/4}) H_D(z^{2/D} W_M^{1/2}) X(z^{2/D} W_M^{-(k+\frac{1}{2})})$$

(3.20)

where (3.3) has been substituted into the appropriate locations. The two signals  $a_k[n]$  and  $a_{k+1}[n]$  are then summed, which gives the recombined two-channel output

$$\tilde{Y}_{k:k+1}(z) = A_k(z) + A_{k+1}(z)

= \frac{1}{D} [H_I(zW_M^{-D/4}) H_D(z^{2/D} W_M^{-1/2})

+ H_I(zW_M^{D/4}) H_D(z^{2/D} W_M^{1/2})] X(z^{2/D} W_M^{-(k+\frac{1}{2})}).$$

(3.21)

The signal  $X(z^{2/D})$  has twice the bandwidth of the signal in each channel, and the modulation term  $W_M^{k+\frac{1}{2}}$  shows that it has been translated from a frequency that lies between the two adjacent bands. If the decimation and interpolation filters,  $H_D(z)$  and  $H_I(z)$ , are designed such that  $H_I(z)$  passes all of the frequency selectivity of  $H_D(z)$  (i.e. the cascading of  $H_D(z)$  and  $H_I(z)$  yields an equivalent filter  $H_D(z)$ ), then this system does approximate the equivalent system of Figure 3.4.

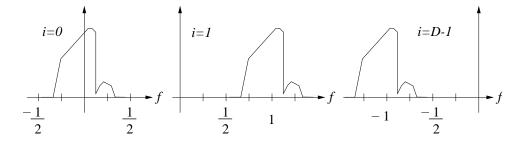

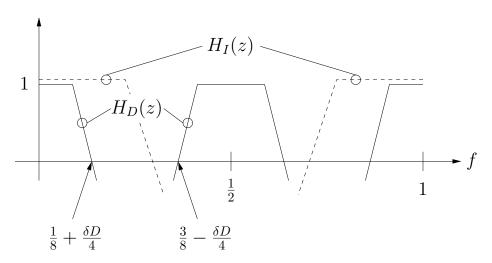

## 3.2.4 Filter design

Attention must now be turned to the design of the filters in the system. An advantage to using this architecture is the fact that there are only two digital filters in the system, which means only two sets of coefficients need to be stored. This is an advantage over most other perfect reconstruction filter banks, which often use a different filter design for each channel. The most critical design will be for  $h_D[n]$  because it determines the performance of the system at the band edges. The lowpass frequency response of  $H_D(f)$  is required to pass the band  $\frac{-1}{2M} \leq f \leq \frac{1}{2M}$  (before the sample rate conversion) and stop everything else with a large amount of attenuation. Due to the fact that digital filters (or any filters, for that matter) cannot be designed to have zero transition bandwidth, it is assumed there is a finite transition bandwidth  $\delta$  in the frequency response of  $h_D[n]$  that needs to be preserved by  $h_I[n]$  as shown in Figure 3.5. The interpolation filter therefore needs to have a passband edge which is above  $\frac{1}{2M} + \frac{\delta}{2}$ . After decimation by a factor of D and upsampling by a factor of 2, the required passband for the design of the interpolation filter becomes  $|f| \geq \frac{D}{4M} + \frac{\delta D}{4}$ . The upsampling also produces an undesired "copy" of the signal band centered at  $f=\frac{1}{2}$ . This copy must be eliminated by the interpolation filter. The requirements of the interpolation filter are that it must pass the desired term centered at f = 0 that covers the range of frequencies  $\frac{-D}{4M} - \frac{\delta D}{4} \le f \le \frac{D}{4M} + \frac{\delta D}{4}$ , and reject the aliased term centered at  $f = \frac{1}{2}$  covering the range  $\frac{1}{2} - (\frac{D}{4M} + \frac{\delta D}{4}) \le f \le \frac{1}{2} + (\frac{D}{4M} + \frac{\delta D}{4})$ . Table 3.1 summarizes the passband and stopband edge requirements for the filter  $h_I[n]$ . The general case for decimation by D is given and the cases for D=M and  $D=\frac{M}{2}$  are evaluated for comparison. As stated in Section 3.2.2, the aliased terms overlap the edges of the desired signal for the case of maximal decimation, which is shown again in the values in the table for the passband and stopband edges of  $h_I[n]$ . The values for decimation by  $D = \frac{M}{2}$  show the spacing between terms (provided that  $\delta M < 1$ ) that eases the filter design. Figure 3.8 further

| decimation rate   | passband                                    | stopband                                                                                                                 |  |

|-------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| D (general)       | $ f  \le \frac{D}{4M} + \frac{\delta D}{4}$ | $\frac{1}{2} - \left(\frac{D}{4M} + \frac{\delta D}{4}\right) \le f \le \frac{1}{2} + \frac{D}{4M} + \frac{\delta D}{4}$ |  |

| D = M             | $ f  \le \frac{1}{4} + \frac{\delta M}{4}$  | $\frac{1}{4} - \frac{\delta M}{4} \le f \le \frac{3}{4} + \frac{\delta M}{4}$                                            |  |

| $D = \frac{M}{2}$ | $ f  \le \frac{1}{8} + \frac{\delta M}{8}$  | $\frac{3}{8} - \frac{\delta M}{8} \le f \le \frac{5}{8} + \frac{\delta M}{8}$                                            |  |

Table 3.1: Requirements of the interpolation filter for different rates of decimation

Figure 3.8: Requirements for interpolation filter  $H_I(z)$  frequency response (for  $D=\frac{M}{2}$ )

Figure 3.9: Multi-stage decimation and filtering

illustrates the filter requirements of  $h_I[n]$  for the case  $D = \frac{M}{2}$ , where the upsampled terms that have been filtered by  $h_D[n]$  are also shown.

The decimation filter  $h_D[n]$  processes every channel with a lowpass response. Since it must be possible to recombine adjacent channels in the reconstruction, the filter  $h_D[n]$  must have a symmetrical design. Due to the high decimation rate, designing filters with passbands that are small relative to the sampling frequency is difficult. Designing these filters with tight specifications in the transition band is even more difficult because the transition band is also small.

### 3.2.4.1 Multistage decimation

The steps in the design process of the filter  $H_D(z)$  are illustrated in Figure 3.9, where the straightforward approach to decimation by D is shown in Figure 3.9(a). The filter design can be simplified if it can be done at a lower sampling rate where the passband and the transition band  $\delta$  take up a larger part of the sampling bandwidth.

By breaking the filter  $h_D[n]$  into two separate filters with one filter each used to process the signal before and after decimation, the design becomes much easier. This method, shown in Figure 3.9(b), divides the responsibilities of the decimation filter between the two new filters,  $H_A(z)$  and  $H_B(z)$ . The filter  $H_A(z)$  that precedes the down-sampling is used to remove any signal components that may alias into the particular band of interest. This filter design focuses on the location of stopbands rather than the symmetric passband edges, which is not a difficult design if the decimation rate is fairly low.

For higher decimation rates the act of down-sampling is often performed by cascading filter and decimation blocks, a technique that is illustrated in Figure 3.9(c). The filter  $H_A(z)$  and the decimation by D has been split into two new stages composed of filters  $H_{D1}(z)$  and  $H_{D2}(z)$  and decimation by factors of  $D_1$  and  $D_2$  (where  $D_1D_2 = D$ ). The complexity of the filter in each stage is reduced by the following stage because the number of aliased bands that must be filtered out at each stage decreases as the number of stages increases. The spacing between these aliased bands therefore increases with the number of decimation stages, which also makes the designs for  $H_{D1}(z)$  and  $H_{D2}(z)$  easier [6].

The filter  $H_B(z)$  at the end of the decimation stage in Figures 3.9(b) and 3.9(c) provides the symmetric edges for recombination. This filter is always implemented at the lowest sampling rate in the two-channel stage, which makes it a much simpler design than the original solution of using a single filter.

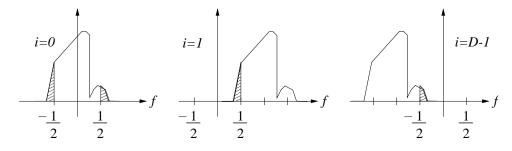

#### 3.2.4.2 Half-band filters

As previously stated, in order to recombine the signals from two neighboring bands, the filter  $H_D(z)$  should have symmetric edges. For a decimation rate of  $D=\frac{M}{2}$  the filtered signal  $\hat{x}_k[n]$  covers the range  $|f| \leq \frac{1}{4} + \frac{\delta M}{4}$ . The filter  $H_D(z)$  must then have symmetric edges about the frequency  $f=\frac{1}{4}$  so that the two signals  $\hat{x}_k[n]$  and  $\hat{x}_{k+1}[n]$  will add together correctly at the band edges. The transition band  $\frac{\delta M}{2}$  should extend

Figure 3.10: Frequency response of a half-band filter

equally into the passband and stopband. The filter bank composed of the two filters represented by the terms  $H_D(z^{2/D}W_M^{1/2})$  and  $H_D(z^{2/D}W_M^{-1/2})$  from (3.21) should be some form of complimentary filter bank. A delay-complimentary filter bank is classified as

$$\sum_{\gamma=0}^{M-1} H_{\gamma}(z) = \beta z^{\alpha} \qquad \beta \neq 0$$

(3.22)

where the filters  $H_{\gamma}(z)$  compose the M-channel filter bank [6]. The filters of a delay-complimentary bank add together to pass the entire sampled bandwidth.

A set of filters called half-band filters meet the above requirements of being symmetric and complimentary. These filters are part of the class of Lth-band filters, which are characterized by having a zero at every Lth coefficient in its impulse response. The term at the origin is a constant, and these requirements are given in the standard equation for even order Lth band filters:

$$h_L[nL] = \begin{cases} \alpha, & n = 0, \\ 0, & \text{otherwise.} \end{cases}$$

(3.23)

Half-band filters are Lth band filters where L=2 and  $\alpha=\frac{1}{2}$ . Since every even indexed coefficient except for  $h_2[0]$  is zero, the polyphase decomposition of  $H_2(z)$  yields

$$H_2(z) = \frac{1}{2} + z^{-1} E_1(z^2)$$

(3.24)

where  $E_1(z)$  is the first polyphase component of  $H_2(z)$ , and the polyphase components of an Lth band filter are found by

$$E_k(z) = \sum_{n=0}^{\infty} h_L[k+nL]z^{-n} \qquad 0 \le k \le L-1.$$

(3.25)

The relation given in (3.24) can be reduced to

$$H_2(z) + H_2(-z) = 1.$$

(3.26)

If  $h_2[n]$  has real coefficients, then  $H_2(-e^{j\omega})=H_2^*(e^{j(\pi-\omega)})$ , and (3.26) gives

$$H_2(e^{j\omega}) + H_2^*(e^{j(\pi-\omega)}) = 1.$$

(3.27)

This equality shows that the half-band filter exhibits symmetry about the quadrature frequency  $\omega=2\pi\left(\frac{1}{4}\right)=\frac{\pi}{2}$  as shown in Figure 3.10. It also shows that the two filters in (3.27) are complimentary. The passband and stopband edges are symmetric with respect to  $\omega=\frac{\pi}{2}$ , meaning that  $\omega_p+\omega_s=\pi$  and  $\omega_s-\omega_p=\delta$ . The filter also has equal passband and stopband ripple [6].

Half-band filters only pass the first half of the sampling bandwidth centered at f=0. The half-band filter is used to set the final signal bandwidth for the channel as shown in Figure 3.7, where for the case  $D=\frac{M}{2}$ , the i=0 term covers the range  $|f|\leq \frac{1}{4}$ , which corresponds to the passband of the half-band filter. The edges of two half-band filters operating on opposite halves of the spectrum add up to a constant across

the transition band, as shown by (3.27). This property is desired of the filter  $H_D(z)$ , and since the last filter in Figure 3.9(c) sets the transition band characteristic, the filter  $H_B(z)$  is chosen to be a half-band filter.

# 3.2.5 Signal delay

The linear phase filters used in this design all impose different sample delays on the signal as it moves through the system. As the signals are modulated in the recombination block, terms are generated that alter the phase of the signals. These terms are scale factors that must be corrected in order to assure that the entire system is linear phase and does not distort the group delay of the signal. A causal filter has linear phase if its impulse response is either symmetric or antisymmetric [6]. Filters that display symmetry can be represented in the form

$$H(z) = z^{-l}H_R(z) (3.28)$$

where l respresents a unit sample delay and  $H_R(z)$  is the real-valued amplitude response of the filter. For a filter of order N (either symmetric or antisymmetric) that has N+1 coefficients, the value of l is given by

$$l = \frac{N}{2}. (3.29)$$

As linear phase filters,  $h_D[n]$  and  $h_I[n]$  can be decomposed as in (3.28) to yield

$$H_D(z) = z^{-l_1} H_{DR}(z)$$

$H_I(z) = z^{-l_2} H_{IR}(z).$  (3.30)

The changes in the phase of the signal as it is processed by the system can be found by substituting (3.30) into (3.19) to find

$$A_{k}(z) = \frac{1}{D} z^{-l_{2}} e^{-j\frac{\pi l_{2}}{4}} H_{IR}(ze^{j\frac{\pi}{4}}) z^{\frac{-2l_{1}}{D}} W_{M}^{\frac{l_{1}}{2}} H_{DR}(z^{2/D} W_{M}^{-1/2}) X(z^{2/D} W_{M}^{-(k+\frac{1}{2})})$$

$$= \frac{1}{D} H_{IR}(zW_{M}^{-D/4}) H_{DR}(z^{2/D} W_{M}^{-1/2}) X(z^{2/D} W_{M}^{-(k+\frac{1}{2})}) z^{-d_{k:k+1}} W_{M}^{c_{k:k+1}}$$

(3.31)

where the cofficients  $d_{k:k+1}$  and  $c_{k:k+1}$  are given by

$$d_{k:k+1} = \frac{2l_1}{D} + l_2$$

$$c_{k:k+1} = \frac{l_1}{2} + \frac{l_2 D}{4}.$$

(3.32)

Similarly, the signal in the opposite channel is found using (3.20) to be

$$A_{k+1}(z) = \frac{1}{D} H_{IR}(zW_M^{D/4}) H_{DR}(z^{2/D}W_M^{1/2}) X(z^{2/D}W_M^{-(k-\frac{1}{2})}) z^{-d_{k:k+1}} W_M^{-c_{k:k+1}}.$$

(3.33)

The phase shift  $W_M^{c_{k:k+1}}$  needs to be corrected in each stage in order to maintain a linear phase characteristic to give the phase corrected recombined output. The signal  $\tilde{y}_{k:k+1}[n]$  becomes

$$\tilde{Y}_{k:k+1}(z) = A_k(z)W_M^{-c_{k:k+1}} + A_{k+1}(z)W_M^{c_{k:k+1}}.$$

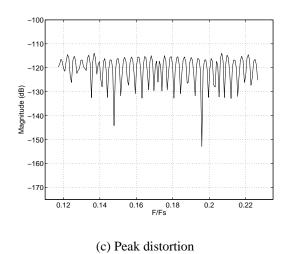

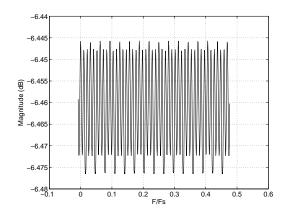

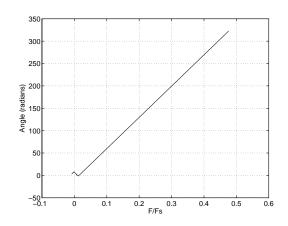

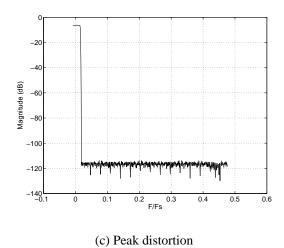

(3.34)