|

CMSIS-Driver

Version 2.7.1

Peripheral Interface for Middleware and Application Code

|

|

CMSIS-Driver

Version 2.7.1

Peripheral Interface for Middleware and Application Code

|

Driver API for NAND Flash Device Interface (Driver_NAND.h). More...

Content | |

| Status Error Codes | |

| Negative values indicate errors (NAND has specific codes in addition to common Status Error Codes). | |

| NAND Events | |

| The NAND driver generates call back events that are notified via the function ARM_NAND_SignalEvent. | |

| NAND Flags | |

| Specify Flag codes. | |

| NAND Control Codes | |

| Many parameters of the NAND driver are configured using the ARM_NAND_Control function. | |

| NAND ECC Codes | |

| Specify ECC codes. | |

| NAND Sequence Execution Codes | |

| Specify execution codes. | |

Data Structures | |

| struct | ARM_NAND_STATUS |

| NAND Status. More... | |

| struct | ARM_DRIVER_NAND |

| Access structure of the NAND Driver. More... | |

| struct | ARM_NAND_CAPABILITIES |

| NAND Driver Capabilities. More... | |

| struct | ARM_NAND_ECC_INFO |

| NAND ECC (Error Correction Code) Information. More... | |

Typedefs | |

| typedef void(* | ARM_NAND_SignalEvent_t )(uint32_t dev_num, uint32_t event) |

| Pointer to ARM_NAND_SignalEvent : Signal NAND Event. More... | |

Functions | |

| ARM_DRIVER_VERSION | ARM_NAND_GetVersion (void) |

| Get driver version. More... | |

| ARM_NAND_CAPABILITIES | ARM_NAND_GetCapabilities (void) |

| Get driver capabilities. More... | |

| int32_t | ARM_NAND_Initialize (ARM_NAND_SignalEvent_t cb_event) |

| Initialize the NAND Interface. More... | |

| int32_t | ARM_NAND_Uninitialize (void) |

| De-initialize the NAND Interface. More... | |

| int32_t | ARM_NAND_PowerControl (ARM_POWER_STATE state) |

| Control the NAND interface power. More... | |

| int32_t | ARM_NAND_DevicePower (uint32_t voltage) |

| Set device power supply voltage. More... | |

| int32_t | ARM_NAND_WriteProtect (uint32_t dev_num, bool enable) |

| Control WPn (Write Protect). More... | |

| int32_t | ARM_NAND_ChipEnable (uint32_t dev_num, bool enable) |

| Control CEn (Chip Enable). More... | |

| int32_t | ARM_NAND_GetDeviceBusy (uint32_t dev_num) |

| Get Device Busy pin state. More... | |

| int32_t | ARM_NAND_SendCommand (uint32_t dev_num, uint8_t cmd) |

| Send command to NAND device. More... | |

| int32_t | ARM_NAND_SendAddress (uint32_t dev_num, uint8_t addr) |

| Send address to NAND device. More... | |

| int32_t | ARM_NAND_ReadData (uint32_t dev_num, void *data, uint32_t cnt, uint32_t mode) |

| Read data from NAND device. More... | |

| int32_t | ARM_NAND_WriteData (uint32_t dev_num, const void *data, uint32_t cnt, uint32_t mode) |

| Write data to NAND device. More... | |

| int32_t | ARM_NAND_ExecuteSequence (uint32_t dev_num, uint32_t code, uint32_t cmd, uint32_t addr_col, uint32_t addr_row, void *data, uint32_t data_cnt, uint8_t *status, uint32_t *count) |

| Execute sequence of operations. More... | |

| int32_t | ARM_NAND_AbortSequence (uint32_t dev_num) |

| Abort sequence execution. More... | |

| int32_t | ARM_NAND_Control (uint32_t dev_num, uint32_t control, uint32_t arg) |

| Control NAND Interface. More... | |

| ARM_NAND_STATUS | ARM_NAND_GetStatus (uint32_t dev_num) |

| Get NAND status. More... | |

| int32_t | ARM_NAND_InquireECC (int32_t index, ARM_NAND_ECC_INFO *info) |

| Inquire about available ECC. More... | |

| void | ARM_NAND_SignalEvent (uint32_t dev_num, uint32_t event) |

| Signal NAND event. More... | |

Driver API for NAND Flash Device Interface (Driver_NAND.h).

NAND devices are a type of non-volatile storage and do not require power to hold data. Wikipedia offers more information about the Flash Memories, including NAND.

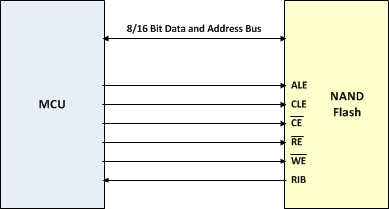

Block Diagram

NAND API

The following header files define the Application Programming Interface (API) for the NAND interface:

The driver implementation is a typical part of the Device Family Pack (DFP) that supports the peripherals of the microcontroller family.

NAND Flash is organized in pages, grouped into blocks as the smallest erasable unit. The addressing of data is archieved by byte_address = block * block_size + page_in_block * page_size + offset_in_page. In terms of this NAND API blocks and pages are referrd to as row and the byte offset within the page as col. Thus one can calculate the byte_address = row * page_size + col. The parameters page_size and block_size are device specific and must be handled by the driver user appropriately.

Driver Functions

The driver functions are published in the access struct as explained in Common Driver Functions

| struct ARM_NAND_STATUS |

| struct ARM_DRIVER_NAND |

Access structure of the NAND Driver.

The functions of the NAND driver are accessed by function pointers exposed by this structure. Refer to Common Driver Functions for overview information.

Each instance of a NAND interface provides such an access structure. The instance is identified by a postfix number in the symbol name of the access structure, for example:

A middleware configuration setting allows connecting the middleware to a specific driver instance Driver_NANDn. The default is 0, which connects a middleware to the first instance of a driver.

Data Fields | |

| ARM_DRIVER_VERSION(* | GetVersion )(void) |

| Pointer to ARM_NAND_GetVersion : Get driver version. More... | |

| ARM_NAND_CAPABILITIES(* | GetCapabilities )(void) |

| Pointer to ARM_NAND_GetCapabilities : Get driver capabilities. More... | |

| int32_t(* | Initialize )(ARM_NAND_SignalEvent_t cb_event) |

| Pointer to ARM_NAND_Initialize : Initialize NAND Interface. More... | |

| int32_t(* | Uninitialize )(void) |

| Pointer to ARM_NAND_Uninitialize : De-initialize NAND Interface. More... | |

| int32_t(* | PowerControl )(ARM_POWER_STATE state) |

| Pointer to ARM_NAND_PowerControl : Control NAND Interface Power. More... | |

| int32_t(* | DevicePower )(uint32_t voltage) |

| Pointer to ARM_NAND_DevicePower : Set device power supply voltage. More... | |

| int32_t(* | WriteProtect )(uint32_t dev_num, bool enable) |

| Pointer to ARM_NAND_WriteProtect : Control WPn (Write Protect). More... | |

| int32_t(* | ChipEnable )(uint32_t dev_num, bool enable) |

| Pointer to ARM_NAND_ChipEnable : Control CEn (Chip Enable). More... | |

| int32_t(* | GetDeviceBusy )(uint32_t dev_num) |

| Pointer to ARM_NAND_GetDeviceBusy : Get Device Busy pin state. More... | |

| int32_t(* | SendCommand )(uint32_t dev_num, uint8_t cmd) |

| Pointer to ARM_NAND_SendCommand : Send command to NAND device. More... | |

| int32_t(* | SendAddress )(uint32_t dev_num, uint8_t addr) |

| Pointer to ARM_NAND_SendAddress : Send address to NAND device. More... | |

| int32_t(* | ReadData )(uint32_t dev_num, void *data, uint32_t cnt, uint32_t mode) |

| Pointer to ARM_NAND_ReadData : Read data from NAND device. More... | |

| int32_t(* | WriteData )(uint32_t dev_num, const void *data, uint32_t cnt, uint32_t mode) |

| Pointer to ARM_NAND_WriteData : Write data to NAND device. More... | |

| int32_t(* | ExecuteSequence )(uint32_t dev_num, uint32_t code, uint32_t cmd, uint32_t addr_col, uint32_t addr_row, void *data, uint32_t data_cnt, uint8_t *status, uint32_t *count) |

| Pointer to ARM_NAND_ExecuteSequence : Execute sequence of operations. More... | |

| int32_t(* | AbortSequence )(uint32_t dev_num) |

| Pointer to ARM_NAND_AbortSequence : Abort sequence execution. More... | |

| int32_t(* | Control )(uint32_t dev_num, uint32_t control, uint32_t arg) |

| Pointer to ARM_NAND_Control : Control NAND Interface. More... | |

| ARM_NAND_STATUS(* | GetStatus )(uint32_t dev_num) |

| Pointer to ARM_NAND_GetStatus : Get NAND status. More... | |

| int32_t(* | InquireECC )(int32_t index, ARM_NAND_ECC_INFO *info) |

| Pointer to ARM_NAND_InquireECC : Inquire about available ECC. More... | |

| ARM_DRIVER_VERSION(* GetVersion)(void) |

Pointer to ARM_NAND_GetVersion : Get driver version.

| ARM_NAND_CAPABILITIES(* GetCapabilities)(void) |

Pointer to ARM_NAND_GetCapabilities : Get driver capabilities.

| int32_t(* Initialize)(ARM_NAND_SignalEvent_t cb_event) |

Pointer to ARM_NAND_Initialize : Initialize NAND Interface.

| int32_t(* Uninitialize)(void) |

Pointer to ARM_NAND_Uninitialize : De-initialize NAND Interface.

| int32_t(* PowerControl)(ARM_POWER_STATE state) |

Pointer to ARM_NAND_PowerControl : Control NAND Interface Power.

| int32_t(* DevicePower)(uint32_t voltage) |

Pointer to ARM_NAND_DevicePower : Set device power supply voltage.

| int32_t(* WriteProtect)(uint32_t dev_num, bool enable) |

Pointer to ARM_NAND_WriteProtect : Control WPn (Write Protect).

| int32_t(* ChipEnable)(uint32_t dev_num, bool enable) |

Pointer to ARM_NAND_ChipEnable : Control CEn (Chip Enable).

| int32_t(* GetDeviceBusy)(uint32_t dev_num) |

Pointer to ARM_NAND_GetDeviceBusy : Get Device Busy pin state.

| int32_t(* SendCommand)(uint32_t dev_num, uint8_t cmd) |

Pointer to ARM_NAND_SendCommand : Send command to NAND device.

| int32_t(* SendAddress)(uint32_t dev_num, uint8_t addr) |

Pointer to ARM_NAND_SendAddress : Send address to NAND device.

| int32_t(* ReadData)(uint32_t dev_num, void *data, uint32_t cnt, uint32_t mode) |

Pointer to ARM_NAND_ReadData : Read data from NAND device.

| int32_t(* WriteData)(uint32_t dev_num, const void *data, uint32_t cnt, uint32_t mode) |

Pointer to ARM_NAND_WriteData : Write data to NAND device.

| int32_t(* ExecuteSequence)(uint32_t dev_num, uint32_t code, uint32_t cmd, uint32_t addr_col, uint32_t addr_row, void *data, uint32_t data_cnt, uint8_t *status, uint32_t *count) |

Pointer to ARM_NAND_ExecuteSequence : Execute sequence of operations.

| int32_t(* AbortSequence)(uint32_t dev_num) |

Pointer to ARM_NAND_AbortSequence : Abort sequence execution.

| int32_t(* Control)(uint32_t dev_num, uint32_t control, uint32_t arg) |

Pointer to ARM_NAND_Control : Control NAND Interface.

| ARM_NAND_STATUS(* GetStatus)(uint32_t dev_num) |

Pointer to ARM_NAND_GetStatus : Get NAND status.

| int32_t(* InquireECC)(int32_t index, ARM_NAND_ECC_INFO *info) |

Pointer to ARM_NAND_InquireECC : Inquire about available ECC.

| struct ARM_NAND_CAPABILITIES |

NAND Driver Capabilities.

A NAND driver can be implemented with different capabilities. The data fields of this struct encode the capabilities implemented by this driver.

Returned by:

| struct ARM_NAND_ECC_INFO |

NAND ECC (Error Correction Code) Information.

Stores the characteristics of a ECC (Error Correction Code) algorithm and provides the information about necessary application data handling in order to protect stored data from NAND bit errors.

ECC algorithms applied on NAND memory typically operate on NAND device page level which is virtually divided to multiple main and spare areas. Data from main and spare area is taken into account when generating ECC data which is also stored into spare area. ECC codeword defines how much data will be protected and how much ECC data will be generated.

To describe how application data must be organized, ECC information structure specifies protection type which defines the protected part of data. As main and spare are of different size, two different algorithms could be provided, we can describe them as ECC0 and ECC1. Type can then have the following values:

| Type | Description |

|---|---|

| 0 | ECC algorithm not used |

| 1 | ECC0 algorithm protects main data |

| 2 | ECC0 algorithm protects main and spare data |

| 3 | ECC0 algorithm protects main and ECC1 algorithm protects spare data |

Virtual page division is described with page layout (page_layout), number of pages (page_count) and virtual page size (page_size or virtual_page_size). Virtual page size used by ECC algorithm can be defined by either page_size or virtual_page_size, depending on the page_size values:

| Value | Main + Spare size |

|---|---|

| 0 | 512 + 16 |

| 1 | 1024 + 32 |

| 2 | 2048 + 64 |

| 3 | 4096 + 128 |

| 4 | 8192 + 256 |

| 8 | 512 + 28 |

| 9 | 1024 + 56 |

| 10 | 2048 + 112 |

| 11 | 4096 + 224 |

| 12 | 8192 + 448 |

| 15 | Not used, use virtual_page_size |

Structure member virtual_page_size is an array of two 16-bit values. First field of array (i.e. virtual_page_size[0]) contains main area size while second (i.e. virtual_page_size[1]) contains spare area size. Number of virtual pages N is defined with page_count and must be calculated as N = 2 ^ page_count.

Page layout defines main and spare ordering and two different page layouts are possible. First ordering assumes that spare area follows after every main area, while in second case all main areas build one contiguous region followed by contiguous region of spare areas. This is defined by member page_layout:

| Layout | Description |

|---|---|

| 0 | Single spare follows after single main: Main0,Spare0 ... MainN-1,SpareN-1 |

| 1 | Contiguous spare follows after contiguous main: Main0 ... MainN-1,Spare0 ... SpareN-1 |

ECC codeword size defines the size of data that is protected by ECC algorithm and is different for main and spare area. All structure members that define the codeword are therefore arrays of two 16-bit values. Codeword offset defines where ECC protected data starts in main (codeword_offset[0]) or spare (codeword_offset[1]) area, codeword size (codeword_size) defines the number of data that is protected i.e. data over which ECC is calculated and codeword gap (codeword_gap) defines the space between two consecutive codeword regions.

Generated ECC data is stored into spare area and is described similar as codeword, with offset from start of spare area (ecc_offset), size of generated data (ecc_size) and gap (ecc_gap) between two consecutive ECC data regions.

Number of bits that ECC algorithm can correct per codeword is defined with correctable_bits.

Parameter for:

| ARM_NAND_SignalEvent_t |

Pointer to ARM_NAND_SignalEvent : Signal NAND Event.

Provides the typedef for the callback function ARM_NAND_SignalEvent.

Parameter for:

| ARM_DRIVER_VERSION ARM_NAND_GetVersion | ( | void | ) |

Get driver version.

The function ARM_NAND_GetVersion returns version information of the driver implementation in ARM_DRIVER_VERSION

Example:

| ARM_NAND_CAPABILITIES ARM_NAND_GetCapabilities | ( | void | ) |

Get driver capabilities.

The function ARM_NAND_GetCapabilities retrieves information about capabilities in this driver implementation. The data fields of the structure ARM_NAND_CAPABILITIES encode various capabilities, for example if a hardware is able to create signal events using the ARM_NAND_SignalEvent callback function.

Example:

| int32_t ARM_NAND_Initialize | ( | ARM_NAND_SignalEvent_t | cb_event | ) |

Initialize the NAND Interface.

| [in] | cb_event | Pointer to ARM_NAND_SignalEvent |

The function ARM_NAND_Initialize initializes the NAND interface. It is called when the middleware component starts operation.

The function performs the following operations:

The parameter cb_event is a pointer to the ARM_NAND_SignalEvent callback function; use a NULL pointer when no callback signals are required.

Example:

| int32_t ARM_NAND_Uninitialize | ( | void | ) |

De-initialize the NAND Interface.

The function ARM_NAND_Uninitialize de-initializes the resources of NAND interface.

It is called when the middleware component stops operation and releases the software resources used by the interface.

| int32_t ARM_NAND_PowerControl | ( | ARM_POWER_STATE | state | ) |

Control the NAND interface power.

| [in] | state | Power state |

The function ARM_NAND_PowerControl controls the power modes of the NAND interface.

The parameter state sets the operation and can have the following values:

Refer to Function Call Sequence for more information.

| int32_t ARM_NAND_DevicePower | ( | uint32_t | voltage | ) |

Set device power supply voltage.

| [in] | voltage | NAND Device supply voltage |

The function ARM_NAND_DevicePower controls the power supply of the NAND device.

The parameter voltage sets the device supply voltage as defined in the table.

AMR_NAND_POWER_xxx_xxx specifies power settings.

| Device Power Bits | Description |

|---|---|

| ARM_NAND_POWER_VCC_OFF | Set VCC Power off |

| ARM_NAND_POWER_VCC_3V3 | Set VCC = 3.3V |

| ARM_NAND_POWER_VCC_1V8 | Set VCC = 1.8V |

| ARM_NAND_POWER_VCCQ_OFF | Set VCCQ I/O Power off |

| ARM_NAND_POWER_VCCQ_3V3 | Set VCCQ = 3.3V |

| ARM_NAND_POWER_VCCQ_1V8 | Set VCCQ = 1.8V |

| ARM_NAND_POWER_VPP_OFF | Set VPP off |

| ARM_NAND_POWER_VPP_ON | Set VPP on |

| int32_t ARM_NAND_WriteProtect | ( | uint32_t | dev_num, |

| bool | enable | ||

| ) |

Control WPn (Write Protect).

| [in] | dev_num | Device number |

| [in] | enable |

|

The function ARM_NAND_WriteProtect controls the Write Protect (WPn) pin of a NAND device.

The parameter dev_num is the device number.

The parameter enable specifies whether to enable or disable write protection.

| int32_t ARM_NAND_ChipEnable | ( | uint32_t | dev_num, |

| bool | enable | ||

| ) |

Control CEn (Chip Enable).

| [in] | dev_num | Device number |

| [in] | enable |

|

The function ARM_NAND_ChipEnable control the Chip Enable (CEn) pin of a NAND device.

The parameter dev_num is the device number.

The parameter enable specifies whether to enable or disable the device.

This function is optional and supported only when the data field ce_manual = 1 in the structure ARM_NAND_CAPABILITIES. Otherwise, the Chip Enable (CEn) signal is controlled automatically by SendCommand/Address, Read/WriteData and ExecuteSequence (for example when the NAND device is connected to a memory bus).

| int32_t ARM_NAND_GetDeviceBusy | ( | uint32_t | dev_num | ) |

Get Device Busy pin state.

| [in] | dev_num | Device number |

The function ARM_NAND_GetDeviceBusy returns the status of the Device Busy pin: [1=busy; 0=not busy or error].

The parameter dev_num is the device number.

| int32_t ARM_NAND_SendCommand | ( | uint32_t | dev_num, |

| uint8_t | cmd | ||

| ) |

Send command to NAND device.

| [in] | dev_num | Device number |

| [in] | cmd | Command |

The function ARM_NAND_SendCommand sends a command to the NAND device.

The parameter dev_num is the device number.

The parameter cmd is the command sent to the NAND device.

| int32_t ARM_NAND_SendAddress | ( | uint32_t | dev_num, |

| uint8_t | addr | ||

| ) |

Send address to NAND device.

| [in] | dev_num | Device number |

| [in] | addr | Address |

Send an address to the NAND device. The parameter dev_num is the device number. The parameter addr is the address.

| int32_t ARM_NAND_ReadData | ( | uint32_t | dev_num, |

| void * | data, | ||

| uint32_t | cnt, | ||

| uint32_t | mode | ||

| ) |

Read data from NAND device.

| [in] | dev_num | Device number |

| [out] | data | Pointer to buffer for data to read from NAND device |

| [in] | cnt | Number of data items to read |

| [in] | mode | Operation mode |

The function ARM_NAND_ReadData reads data from a NAND device.

The parameter dev_num is the device number.

The parameter data is a pointer to the buffer that stores the data read from a NAND device.

The parameter cnt is the number of data items to read.

The parameter mode defines the operation mode as listed in the table below.

| Read Data Mode | Description |

|---|---|

| ARM_NAND_ECC(n) | Select ECC |

| ARM_NAND_ECC0 | Use ECC0 of selected ECC |

| ARM_NAND_ECC1 | Use ECC1 of selected ECC |

| ARM_NAND_DRIVER_DONE_EVENT | Generate ARM_NAND_EVENT_DRIVER_DONE |

The data item size is defined by the data type, which depends on the configured data bus width.

Data type is:

The function executes in the following ways:

| int32_t ARM_NAND_WriteData | ( | uint32_t | dev_num, |

| const void * | data, | ||

| uint32_t | cnt, | ||

| uint32_t | mode | ||

| ) |

Write data to NAND device.

| [in] | dev_num | Device number |

| [out] | data | Pointer to buffer with data to write to NAND device |

| [in] | cnt | Number of data items to write |

| [in] | mode | Operation mode |

The function ARM_NAND_WriteData writes data to a NAND device.

The parameter dev_num is the device number.

The parameter data is a pointer to the buffer with data to write.

The parameter cnt is the number of data items to write.

The parameter mode defines the operation mode as listed in the table below.

| Write Data Mode | Description |

|---|---|

| ARM_NAND_ECC(n) | Select ECC |

| ARM_NAND_ECC0 | Use ECC0 of selected ECC |

| ARM_NAND_ECC1 | Use ECC1 of selected ECC |

| ARM_NAND_DRIVER_DONE_EVENT | Generate ARM_NAND_EVENT_DRIVER_DONE |

The data item size is defined by the data type, which depends on the configured data bus width.

Data type is:

The function executes in the following ways:

| int32_t ARM_NAND_ExecuteSequence | ( | uint32_t | dev_num, |

| uint32_t | code, | ||

| uint32_t | cmd, | ||

| uint32_t | addr_col, | ||

| uint32_t | addr_row, | ||

| void * | data, | ||

| uint32_t | data_cnt, | ||

| uint8_t * | status, | ||

| uint32_t * | count | ||

| ) |

Execute sequence of operations.

| [in] | dev_num | Device number |

| [in] | code | Sequence code |

| [in] | cmd | Command(s) |

| [in] | addr_col | Column address |

| [in] | addr_row | Row address |

| [in,out] | data | Pointer to data to be written or read |

| [in] | data_cnt | Number of data items in one iteration |

| [out] | status | Pointer to status read |

| [in,out] | count | Number of iterations |

The function ARM_NAND_ExecuteSequence executes a sequence of operations for a NAND device.

The parameter dev_num is the device number.

The parameter code is the sequence encoding as defined in the table Sequence execution Code.

The parameter cmd is the command or a series of commands.

The parameter addr_col is the column address.

The parameter addr_row is the row address.

The parameter data is a pointer to the buffer that stores the data to or loads the data from.

The parameter data_cnt is the number of data items to read or write in one iteration.

The parameter status is a pointer to the buffer that stores the status read.

The parameter count is a pointer to the number of iterations.

ARM_NAND_CODE_xxx specifies sequence execution codes.

| Sequence Execution Code | Description |

|---|---|

| ARM_NAND_CODE_SEND_CMD1 | Send Command 1 (cmd[7..0]) |

| ARM_NAND_CODE_SEND_ADDR_COL1 | Send Column Address 1 (addr_col[7..0]) |

| ARM_NAND_CODE_SEND_ADDR_COL2 | Send Column Address 2 (addr_col[15..8]) |

| ARM_NAND_CODE_SEND_ADDR_ROW1 | Send Row Address 1 (addr_row[7..0]) |

| ARM_NAND_CODE_SEND_ADDR_ROW2 | Send Row Address 2 (addr_row[15..8]) |

| ARM_NAND_CODE_SEND_ADDR_ROW3 | Send Row Address 3 (addr_row[23..16]) |

| ARM_NAND_CODE_INC_ADDR_ROW | Auto-increment Row Address |

| ARM_NAND_CODE_WRITE_DATA | Write Data |

| ARM_NAND_CODE_SEND_CMD2 | Send Command 2 (cmd[15..8]) |

| ARM_NAND_CODE_WAIT_BUSY | Wait while R/Bn busy |

| ARM_NAND_CODE_READ_DATA | Read Data |

| ARM_NAND_CODE_SEND_CMD3 | Send Command 3 (cmd[23..16]) |

| ARM_NAND_CODE_READ_STATUS | Read Status byte and check FAIL bit (bit 0) |

| ARM_NAND_ECC(n) | Select ECC |

| ARM_NAND_ECC0 | Use ECC0 of selected ECC |

| ARM_NAND_ECC1 | Use ECC1 of selected ECC |

| ARM_NAND_DRIVER_DONE_EVENT | Generate ARM_NAND_EVENT_DRIVER_DONE |

The data item size is defined by the data type, which depends on the configured data bus width.

Data type is:

The function is non-blocking and returns as soon as the driver has started executing the specified sequence. When the operation is completed, the ARM_NAND_EVENT_DRIVER_DONE event is generated (if enabled by ARM_NAND_DRIVER_DONE_EVENT). Progress of the operation can also be monitored by calling the ARM_NAND_GetStatus function and checking the busy data field.

Driver executes the number of specified iterations where in each iteration items specified by ARM_NAND_CODE_xxx are executed in the order as listed in the table Sequence execution Code. The parameter count is holding the current number of iterations left.

Execution is automatically aborted and ARM_NAND_EVENT_DRIVER_DONE event is generated (if enabled by ARM_NAND_DRIVER_DONE_EVENT):

| int32_t ARM_NAND_AbortSequence | ( | uint32_t | dev_num | ) |

Abort sequence execution.

| [in] | dev_num | Device number |

The function ARM_NAND_AbortSequence aborts execution of the current sequence for a NAND device.

The parameter dev_num is the device number.

| int32_t ARM_NAND_Control | ( | uint32_t | dev_num, |

| uint32_t | control, | ||

| uint32_t | arg | ||

| ) |

Control NAND Interface.

| [in] | dev_num | Device number |

| [in] | control | Operation |

| [in] | arg | Argument of operation |

The function ARM_NAND_Control controls the NAND interface and executes operations.

The parameter dev_num is the device number.

The parameter control specifies the operation.

The parameter arg provides (depending on the control) additional information or sets values.

The table lists the operations for the parameter control.

| Parameter control | Operation |

|---|---|

| ARM_NAND_BUS_MODE | Set the bus mode. The parameter arg sets the Bus Mode. |

| ARM_NAND_BUS_DATA_WIDTH | Set the data bus width. The parameter arg sets the Bus Data Width. |

| ARM_NAND_DRIVER_STRENGTH | Set the driver strength. The parameter arg sets the Driver Strength. |

| ARM_NAND_DRIVER_READY_EVENT | Control generation of callback event ARM_NAND_EVENT_DRIVER_READY. Enable: arg = 1. Disable: arg = 0. |

| ARM_NAND_DEVICE_READY_EVENT | Control generation of callback event ARM_NAND_EVENT_DEVICE_READY; Enable: arg = 1. Disable: arg = 0. |

See Also

The table lists values for the parameter arg used with the control operation ARM_NAND_BUS_MODE, ARM_NAND_BUS_DATA_WIDTH, and ARM_NAND_DRIVER_STRENGTH. Values from different categories can be ORed.

| Parameter arg for control = ARM_NAND_BUS_MODE | Bit | Category | Description | Supported when ARM_NAND_CAPABILITIES |

|---|---|---|---|---|

| ARM_NAND_BUS_TIMING_MODE_0 (default) | 0..3 | Bus Timing Mode | 0 | The maximum timing mode that can be applied to a specific Bus Data Interface is stored in the data fields: sdr_timing_mode - for SDR ddr_timing_mode - for NV-DDR ddr2_timing_mode - for NV_DDR2 |

| ARM_NAND_BUS_TIMING_MODE_1 | 1 | |||

| ARM_NAND_BUS_TIMING_MODE_2 | 2 | |||

| ARM_NAND_BUS_TIMING_MODE_3 | 3 | |||

| ARM_NAND_BUS_TIMING_MODE_4 | 4 (SDR EDO capable) | |||

| ARM_NAND_BUS_TIMING_MODE_5 | 5 (SDR EDO capable) | |||

| ARM_NAND_BUS_TIMING_MODE_6 | 6 (NV-DDR2 only) | |||

| ARM_NAND_BUS_TIMING_MODE_7 | 7 (NV-DDR2 only) | |||

| ARM_NAND_BUS_SDR (default) | 4..7 | Bus Data Interface | SDR (Single Data Rate) - Traditional interface | always supported |

| ARM_NAND_BUS_DDR | NV-DDR (Double Data Rate) | data field ddr = 1 | ||

| ARM_NAND_BUS_DDR2 | NV-DDR2 (Double Data Rate) | data field ddr2 = 1 | ||

| ARM_NAND_BUS_DDR2_DO_WCYC_0 (default) | 8..11 | Data Output Warm-up | Set the DDR2 Data Output Warm-up to 0 cycles | Data Output Warm-up cycles are dummy cycles for interface calibration with no incremental data transfer and apply to NV-DDR2 of the Bus Data Interface. |

| ARM_NAND_BUS_DDR2_DO_WCYC_1 | Set the DDR2 Data Output Warm-up to 1 cycles | |||

| ARM_NAND_BUS_DDR2_DO_WCYC_2 | Set the DDR2 Data Output Warm-up to 2 cycles | |||

| ARM_NAND_BUS_DDR2_DO_WCYC_4 | Set the DDR2 Data Output Warm-up to 4 cycles | |||

| ARM_NAND_BUS_DDR2_DI_WCYC_0 (default) | 12..15 | Data Input Warm-up | Set the DDR2 Data Input Warm-up to 0 cycles | Data Input Warm-up cycles are dummy cycles for interface calibration with no incremental data transfer and apply to NV-DDR2 of the Bus Data Interface. |

| ARM_NAND_BUS_DDR2_DI_WCYC_1 | Set the DDR2 Data Input Warm-up to 1 cycles | |||

| ARM_NAND_BUS_DDR2_DI_WCYC_2 | Set the DDR2 Data Input Warm-up to 2 cycles | |||

| ARM_NAND_BUS_DDR2_DI_WCYC_4 | Set the DDR2 Data Input Warm-up to 4 cycles | |||

| ARM_NAND_BUS_DDR2_VEN | 16 | Miscellaneous | Set the DDR2 Enable external VREFQ as reference | |

| ARM_NAND_BUS_DDR2_CMPD | 17 | Set the DDR2 Enable complementary DQS (DQS_c) signal | ||

| ARM_NAND_BUS_DDR2_CMPR | 18 | Set the DDR2 Enable complementary RE_n (RE_c) signal | ||

| Parameter arg for control = ARM_NAND_BUS_DATA_WIDTH | Bit | Category | Description | Supported when ARM_NAND_CAPABILITIES |

| ARM_NAND_BUS_DATA_WIDTH_8 (default) | 0..1 | Bus Data Width | Set to 8 bit | always supported |

| ARM_NAND_BUS_DATA_WIDTH_16 | Set to 16 bit | data field data_width_16 = 1 | ||

| Parameter arg for control = ARM_NAND_DRIVER_STRENGTH | Bit | Category | Description | Supported when ARM_NAND_CAPABILITIES |

| ARM_NAND_DRIVER_STRENGTH_18 | 0..3 | Driver Strength | Set the Driver Strength 2.0x = 18 Ohms | data field driver_strength_18 = 1 |

| ARM_NAND_DRIVER_STRENGTH_25 | Set the Driver Strength 1.4x = 25 Ohms | data field driver_strength_25 = 1 | ||

| ARM_NAND_DRIVER_STRENGTH_35 (default) | Set the Driver Strength 1.0x = 35 Ohms | always supported | ||

| ARM_NAND_DRIVER_STRENGTH_50 | Set the Driver Strength 0.7x = 50 Ohms | data field driver_strength_50 = 1 |

Example

| ARM_NAND_STATUS ARM_NAND_GetStatus | ( | uint32_t | dev_num | ) |

Get NAND status.

| [in] | dev_num | Device number |

The function ARM_NAND_GetStatus returns the current NAND device status.

The parameter dev_num is the device number.

| int32_t ARM_NAND_InquireECC | ( | int32_t | index, |

| ARM_NAND_ECC_INFO * | info | ||

| ) |

Inquire about available ECC.

| [in] | index | Inquire ECC index |

| [out] | info | Pointer to ECC information ARM_NAND_ECC_INFO retrieved |

The function ARM_NAND_InquireECC reads error correction code information.

The parameter index is the ECC index and is used to retrieve different ECC configurations.

The parameter info is a pointer of type ARM_NAND_ECC_INFO. The data fields store the information.

When multiple different ECC configurations exist, ARM_NAND_ECC_INFO structure exists for each configuration. Parameter index denotes which configuration will be retrieved. Value of index should start with zero to retrieve first ECC configuration and should be incremented in order to retrieve next ECC configuration. When index is out of range function ARM_NAND_InquireECC returns with error.

Parameter index is used by ARM_NAND_ECC(n) in ARM_NAND_ReadData, ARM_NAND_WriteData and ARM_NAND_ExecuteSequence to select suitable ECC configuration.

Example

| void ARM_NAND_SignalEvent | ( | uint32_t | dev_num, |

| uint32_t | event | ||

| ) |

Signal NAND event.

| [in] | dev_num | Device number |

| [in] | event | Event notification mask |

The function ARM_NAND_SignalEvent is a callback function registered by the function ARM_NAND_Initialize.

The parameter dev_num is the device number.

The parameter event indicates one or more events that occurred during driver operation. Each event is encoded in a separate bit and therefore it is possible to signal multiple events within the same call.

Not every event is necessarily generated by the driver. This depends on the implemented capabilities stored in the data fields of the structure ARM_NAND_CAPABILITIES, which can be retrieved with the function ARM_NAND_GetCapabilities.

The following events can be generated:

| Parameter event | Bit | Description |

|---|---|---|

| ARM_NAND_EVENT_DEVICE_READY | 0 | Occurs when rising edge is detected on R/Bn (Ready/Busy) pin indicating that the device is ready. |

| ARM_NAND_EVENT_DRIVER_READY | 1 | Occurs to indicate that commands can be executed (after previously being busy and not able to start the requested operation). |

| ARM_NAND_EVENT_DRIVER_DONE | 2 | Occurs after an operation completes. An operation was successfully started before with ARM_NAND_ReadData, ARM_NAND_WriteData, ARM_NAND_ExecuteSequence. |

| ARM_NAND_EVENT_ECC_ERROR | 3 | Occurs when ECC generation failed or ECC correction failed. An operation was successfully started before with ARM_NAND_ReadData, ARM_NAND_WriteData, ARM_NAND_ExecuteSequence. |

The event ARM_NAND_EVENT_DEVICE_READY occurs after complete execution of commands (initiated with the functions ARM_NAND_SendCommand, ARM_NAND_SendAddress, ARM_NAND_ReadData, ARM_NAND_WriteData, ARM_NAND_ExecuteSequence). It is useful to indicate completion of complex operations (such as erase). The event is only generated when ARM_NAND_GetCapabilities returns data field event_device_ready = 1 and was enabled by calling ARM_NAND_Control (ARM_NAND_DEVICE_READY_EVENT, 1). If the event is not available, poll the busy data field using the function ARM_NAND_GetStatus.

The event ARM_NAND_EVENT_DRIVER_READY occurs when previously a function (ARM_NAND_SendCommand, ARM_NAND_SendAddress, ARM_NAND_ReadData, ARM_NAND_WriteData, ARM_NAND_ExecuteSequence) returned with ARM_DRIVER_ERROR_BUSY. It is useful when functions are called simultaneously from independent threads (for example to control multiple devices) and the threads have no knowledge about each other (driver rejects reentrant calls with return of ARM_DRIVER_ERROR_BUSY). dev_num indicates the device that returned previously busy.